MIC68400-1.0YML TR Micrel Inc, MIC68400-1.0YML TR Datasheet - Page 12

MIC68400-1.0YML TR

Manufacturer Part Number

MIC68400-1.0YML TR

Description

IC REG LDO SEQ 4A 1.0V 16-MLF

Manufacturer

Micrel Inc

Datasheet

1.MIC68400-1.8YML_TR.pdf

(15 pages)

Specifications of MIC68400-1.0YML TR

Regulator Topology

Positive Fixed

Voltage - Output

1V

Voltage - Input

1.65 ~ 5.5 V

Voltage - Dropout (typical)

0.36V @ 4A

Number Of Regulators

1

Current - Output

3A

Current - Limit (min)

4A

Operating Temperature

-40°C ~ 125°C

Mounting Type

Surface Mount

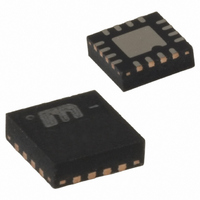

Package / Case

16-MLF®, QFN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

MIC68400-1.0YMLTR

MIC68400-1.0YMLTR

MIC68400-1.0YMLTR

Ramp Up: Cap Controlled Slew Rate

If a capacitor is connected to RC, the bidirectional

current source will charge the cap during startup and

discharge the cap during shutdown. The size of the

capacitor and the RC current (1µA nom) control the

slew rate of the output voltage during startup. For

example, to ramp up a 1.8V regulator from zero to full

output in 10mSec requires a 5.6nF capacitor.

For Fixed Versions:

Similarly, to slew an adjustable (any output voltage)

from 0 to full output in 10mSec requires a 20nF cap.

For Adjustable Versions:

Ramp Down: Turn Off Slew Rate

When EN is lowered and the DLY pin has discharged,

the RC pin and the OUT pin slew toward zero. For

fixed voltage devices, the RC pin slew rate is 2 to 3

times the SR

devices the RC pin slew is much higher. In both

cases, turn off slew rate may be determined by the

RC pin for low values of output capacitor, or by the

maximum discharge current available at the output for

large values of output capacitor. Turn off slew rate is

not a specified characteristic of the MIC68400.

Sequencing Configurations

Sequencing refers to timing based Master/Slave

control between regulators. It allows a Master device

to control the start and stop timing of a single or

multiple Slave devices. In typical sequencing the

Master POR drives the Slave EN. The sequence

begins with the Master EN driven high. The Master

output ramps up and triggers the Master DLY when

the Master output reaches 90%. The Master DLY then

determines when the POR is released to enable the

Slave device. When the Master EN is driven low, the

Master POR is immediately pulled low causing the

Slave to ramp down. However, the Master output will

not ramp down until the Master DLY has fully

discharged. In this way, the Master power can remain

good after the Slave has been ramped down.

In sequencing configurations the Master DLY controls

the turn-on time of the Slave and the Slave DLY

controls the turn-off time of the Slave.

Micrel, Inc.

August 2009

T

T

RC

RC

=

ON

=

0

5 .

V

V

defined above. For adjustable voltage

OUT

⎛

⎜ ⎜

⎝

C

1

μ

RC

⎛

⎜ ⎜

⎝

A

C

1

⎞

⎟ ⎟

⎠

μ

RC

A

SR

⎞

⎟ ⎟

⎠

ON

SR

=

2V

ON

OUT

=

⎛

⎜

⎜

⎝

⎛

⎜

⎜

⎝

C

1

C

1

μ

RC

μ

RC

A

A

⎞

⎟

⎟

⎠

⎞

⎟

⎟

⎠

12

CDlyS > CDlyM

CDlyS < CDlyM

Sequencing Connections

Windowed Sequencing

Delayed Sequencing

[CDlyS=2nF; CDlyM=1nF]

[CDlyS=1nF; CDlyM=2nF]

M9999-081809-C

MIC68400