PIC12C672/JW Microchip Technology, PIC12C672/JW Datasheet - Page 74

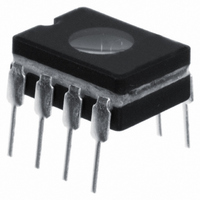

PIC12C672/JW

Manufacturer Part Number

PIC12C672/JW

Description

IC MCU EPROM 2KX14 A/D 8CDIP

Manufacturer

Microchip Technology

Series

PIC® 12Cr

Datasheets

1.PIC16F688T-ISL.pdf

(688 pages)

2.PIC12CE673-10P.pdf

(129 pages)

3.PIC12CE673-10P.pdf

(14 pages)

Specifications of PIC12C672/JW

Core Processor

PIC

Core Size

8-Bit

Speed

10MHz

Peripherals

POR, WDT

Number Of I /o

5

Program Memory Size

3.5KB (2K x 14)

Program Memory Type

EPROM, UV

Ram Size

128 x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 4x8b

Oscillator Type

Internal

Operating Temperature

0°C ~ 70°C

Package / Case

8-CDIP (0.300", 7.62mm) Window

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Eeprom Size

-

Connectivity

-

Other names

Q395827

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

PIC12C672/JW

Manufacturer:

MICKO

Quantity:

2 100

- Current page: 74 of 688

- Download datasheet (3Mb)

PICmicro MID-RANGE MCU FAMILY

4.3

DS31004A-page 4-6

1. MOVLW 55h

2. MOVWF PORTB

3. CALL SUB_1

4. BSF

5. Instruction @ address SUB_1

All instructions are single cycle, except for any program branches. These take two cycles since the fetch

instruction is “flushed” from the pipeline while the new instruction is being fetched and then executed.

Instruction Flow/Pipelining

PORTA, BIT3 (Forced NOP)

An “Instruction Cycle” consists of four Q cycles (Q1, Q2, Q3, and Q4). Fetch takes one instruction

cycle while decode and execute takes another instruction cycle. However, due to Pipelining, each

instruction effectively executes in one cycle. If an instruction causes the program counter to

change (e.g. GOTO) then an extra cycle is required to complete the instruction

The instruction fetch begins with the program counter incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the “Instruction Register (IR)” in

cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data

memory is read during Q2 (operand read) and written during Q4 (destination write).

Example 4-1

At time T

tion executes while the second instruction is fetched. During T

cutes while the third instruction is fetched. During T

third instruction (CALL SUB_1) is executed. When the third instruction completes execution, the

CPU forces the address of instruction four onto the Stack and then changes the Program Counter

(PC) to the address of SUB_1. This means that the instruction that was fetched during T

to be “flushed” from the pipeline. During T

the instruction at address SUB_1 is fetched. Finally during T

the instruction at address SUB_1 + 1 is fetched.

Example 4-1: Instruction Pipeline Flow

Fetch 1

CY

T

CY

0, the first instruction is fetched from program memory. During T

shows the operation of the two stage pipeline for the instruction sequence shown.

0

Execute 1

Fetch 2

T

CY

1

Execute 2

Fetch 3

T

CY

CY

2

4, instruction four is flushed (executed as a NOP) and

Execute 3

Fetch 4

CY

T

CY

3, the fourth instruction is fetched while the

3

CY

Fetch SUB_1 Execute SUB_1

5, instruction five is executed and

CY

Flush

T

2, the second instruction exe-

CY

1997 Microchip Technology Inc.

4

CY

Fetch SUB_1 + 1

1, the first instruc-

(Example

T

CY

CY

5

3 needs

4-1).

Related parts for PIC12C672/JW

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

8-Pin/ 8-Bit CMOS Microcontroller with EEPROM Data Memory

Manufacturer:

Microchip Technology

Part Number:

Description:

IC, 8BIT MCU, PIC12, 32MHZ, DFN-8

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

IC, 8BIT MCU, PIC12, 32MHZ, DFN-8

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet: