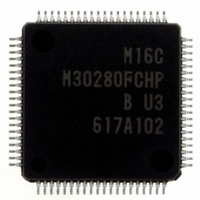

M30280FCHP#U3B Renesas Electronics America, M30280FCHP#U3B Datasheet - Page 222

M30280FCHP#U3B

Manufacturer Part Number

M30280FCHP#U3B

Description

IC M16C/28 MCU FLASH 128K 80LQFP

Manufacturer

Renesas Electronics America

Series

M16C™ M16C/Tiny/28r

Datasheet

1.M30280F6HPU9.pdf

(425 pages)

Specifications of M30280FCHP#U3B

Core Processor

M16C/60

Core Size

16-Bit

Speed

20MHz

Connectivity

I²C, IEBus, SIO, UART/USART

Peripherals

DMA, POR, PWM, Voltage Detect, WDT

Number Of I /o

71

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

12K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 24x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-LQFP

For Use With

R0K330290S000BE - KIT EVAL STARTER FOR M16C/29M30290T2-CPE - EMULATOR COMPACT M16C/26A/28/29M30290T2-CPE-HP - EMULATOR COMPACT FOR M16C/TINY

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

M30280FCHP#U3BM30280FCHP#U5B

Manufacturer:

Renesas Electronics America

Quantity:

135

Part Number:

M30280FCHP#U3BM30280FCHP#U5B

Manufacturer:

Renesas Electronics America

Quantity:

10 000

Part Number:

M30280FCHP#U3BM30280FCHP#U7B

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 222 of 425

- Download datasheet (4Mb)

M

R

R

1

e

E

6

. v

J

C

0

2

9

2 /

0 .

B

14.1.3.7 ACK and NACK

14.1.3.8 Initialization of Transmission/Reception

8

0

0

0

If the STSPSEL bit in the U2SMR4 register is set to “0” (start and stop conditions not generated) and

the ACKC bit in the U2SMR4 register is set to “1” (ACK data output), the value of the ACKD bit in the

U2SMR4 register is output from the SDA

If the IICM2 bit is set to "0", a NACK interrupt request is generated if the SDA

rising edge of the 9th bit of transmit clock pulse. An ACK interrupt request is generated if the SDA

is low at the rising edge of the 9th bit of transmit clock pulse.

If ACK2 is selected for the cause of DMA1 request, a DMA transfer can be activated by detection of an

acknowledge.

If a start condition is detected while the STAC bit is set to "1" (UART2 initialization enabled), the serial

I/O operates as described below.

- The transmit shift register is initialized, and the content of the U2TB register is transferred to the

- The receive shift register is initialized, and the serial I/O starts receiving data synchronously with the

- The SWC bit is set to “1” (SCL

Note that when UART2 transmission/reception is started using this function, the TI does not change

state. Note also that when using this function, the selected transfer clock should be an external clock.

G

4

transmit shift register. In this way, the serial I/O starts sending data synchronously with the next clock

when a start condition was detected until the first bit in the data is output synchronously with the input

J

pulse applied. However, the UART2 output value does not change state and remains the same as

clock.

next clock pulse applied.

falling edge of the ninth clock pulse.

7

o r

a

0 -

. n

u

2

p

3

0

, 1

0

(

M

2

1

0

6

0

7

C

2 /

, 8

page 200

M

1

6

C

2 /

f o

8

3

) B

8

5

2

wait output enabled). Consequently, the SCL

2

pin.

2

2

pin remains high at the

pin is pulled low at the

14. Serial I/O

2

pin

Related parts for M30280FCHP#U3B

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: