AT91SAM7X128B-CU-999 Atmel, AT91SAM7X128B-CU-999 Datasheet - Page 16

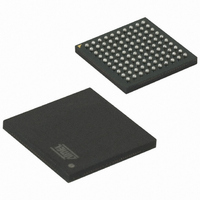

AT91SAM7X128B-CU-999

Manufacturer Part Number

AT91SAM7X128B-CU-999

Description

IC MCU ARM 128KB FLASH 100TFBGA

Manufacturer

Atmel

Series

AT91SAMr

Datasheet

1.AT91SAM7X256B-CU.pdf

(45 pages)

Specifications of AT91SAM7X128B-CU-999

Core Processor

ARM7

Core Size

16/32-Bit

Speed

55MHz

Connectivity

CAN, Ethernet, I²C, SPI, SSC, UART/USART, USB

Peripherals

Brown-out Detect/Reset, DMA, POR, PWM, WDT

Number Of I /o

62

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 1.95 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Processor Series

AT91SAMx

Core

ARM7TDMI

Data Bus Width

32 bit

Data Ram Size

32 KB

Interface Type

CAN, I2S, JTAG, UASRT

Maximum Clock Frequency

55 MHz

Operating Supply Voltage

3.3 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

JTRACE-ARM-2M, KSK-AT91SAM7X-PL, MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

AT91SAM-ICE, AT91-ISP, AT91SAM7X-EK

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

7.4

16

Peripheral DMA Controller

AT91SAM7X512/256/128 Preliminary

• Embedded Flash Controller

• Handles data transfer between peripherals and memories

• Thirteen channels

• Low bus arbitration overhead

• Next Pointer management for reducing interrupt latency requirements

• Peripheral DMA Controller (PDC) priority is as follows (from the highest priority to the lowest):

– Embedded Flash interface, up to three programmable wait states

– Prefetch buffer, buffering and anticipating the 16-bit requests, reducing the required

– Key-protected program, erase and lock/unlock sequencer

– Single command for erasing, programming and locking operations

– Interrupt generation in case of forbidden operation

– Two for each USART

– Two for the Debug Unit

– Two for the Serial Synchronous Controller

– Two for each Serial Peripheral Interface

– One for the Analog-to-digital Converter

– One Master Clock cycle needed for a transfer from memory to peripheral

– Two Master Clock cycles needed for a transfer from peripheral to memory

wait states

Receive

Receive

Receive

Receive

Receive

Receive

Receive

Transmit

Transmit

Transmit

Transmit

Transmit

Transmit

DBGU

USART0

USART1

SSC

ADC

SPI0

SPI1

DBGU

USART0

USART

SSC

SPI0

SPI1

6120FS–ATARM–17-Feb-09