ATMEGA48P-20MMUR Atmel, ATMEGA48P-20MMUR Datasheet

ATMEGA48P-20MMUR

Specifications of ATMEGA48P-20MMUR

Related parts for ATMEGA48P-20MMUR

ATMEGA48P-20MMUR Summary of contents

Page 1

... • Speed Grade: – ATmega48P/88P/168PV MHz @ 1.8 - 5.5V MHz @ 2.7 - 5.5V – ATmega48P/88P/168P MHz @ 2.7 - 5.5V MHz @ 4.5 - 5.5V • Low Power Consumption at 1 MHz, 1.8V, 25°C: – Active Mode: 0.3 mA – Power-down Mode: 0.1 µA – Power-save Mode: 0.8 µA (Including 32 kHz RTC) Note: 1 ...

Page 2

... Pin Configurations Figure 1-1. Pinout ATmega48P/88P/168P TQFP Top View (PCINT19/OC2B/INT1) PD3 1 (PCINT20/XCK/T0) PD4 2 GND 3 VCC 4 GND 5 VCC 6 (PCINT6/XTAL1/TOSC1) PB6 7 (PCINT7/XTAL2/TOSC2) PB7 8 28 MLF Top View (PCINT19/OC2B/INT1) PD3 1 (PCINT20/XCK/T0) PD4 2 VCC 3 GND 4 (PCINT6/XTAL1/TOSC1) PB6 5 (PCINT7/XTAL2/TOSC2) PB7 6 (PCINT21/OC0B/T1) PD5 7 NOTE: Bottom pad should be soldered to ground. ...

Page 3

... The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running. 8025L–AVR–7/10 ”System Clock and Clock Options” on page Table 28-3 on page ATmega48P/88P/168P ”Alternate Functions of Port B” on page 27. 314. Shorter pulses are not guaran- ”Alternate Functions of Port C” on page ...

Page 4

... These pins are powered from the analog supply and serve as 10-bit ADC channels. 2. Overview The ATmega48P/88P/168P is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega48P/88P/168P achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed. 8025L– ...

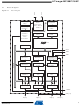

Page 5

... USART 0 PORT D (8) 8025L–AVR–7/10 Power Timer Supervision POR / BOD & RESET Flash Clock 16bit T/C 1 Analog Comp. SPI PORT B (8) PD[0..7] PB[0..7] ATmega48P/88P/168P debugWIRE PROGRAM LOGIC SRAM CPU AVCC AREF GND 2 A/D Conv. Internal 6 Bandgap TWI PORT C (7) RESET XTAL[1 ...

Page 6

... Atmel ATmega48P/88P/168P is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications. The ATmega48P/88P/168P AVR is supported with a full suite of program and system develop- ment tools including: C Compilers, Macro Assemblers, Program Debugger/Simulators, In-Circuit Emulators, and Evaluation kits. ...

Page 7

... In ATmega48P, there is no Read-While-Write support and no separate Boot Loader Section. The SPM instruction can execute from the entire Flash. 8025L–AVR–7/10 ATmega48P/88P/168P 7 ...

Page 8

... For I/O Registers located in extended I/O map, “IN”, “OUT”, “SBIS”, “SBIC”, “CBI”, and “SBI” instructions must be replaced with instructions that allow access to extended I/O. Typically “LDS” and “STS” combined with “SBRS”, “SBRC”, “SBR”, and “CBR”. 8025L–AVR–7/10 1. ATmega48P/88P/168P 8 ...

Page 9

... This allows single-cycle Arithmetic Logic Unit (ALU) operation typ- 8025L–AVR–7/10 Block Diagram of the AVR Architecture Program Flash Counter Program Memory Instruction Register Instruction Decoder Control Lines ATmega48P/88P/168P Data Bus 8-bit Status and Control Interrupt Unit General Purpose SPI Registrers Unit Watchdog ...

Page 10

... SPI, and other I/O functions. The I/O Memory can be accessed directly the Data Space locations following those of the Register File, 0x20 - 0x5F. In addition, the ATmega48P/88P/168P has Extended I/O space from 0x60 - 0xFF in SRAM where only the ST/STS/STD and LD/LDS/LDD instructions can be used. ...

Page 11

... Set Description” for detailed information. • Bit 0 – C: Carry Flag The Carry Flag C indicates a carry in an arithmetic or logic operation. See the “Instruction Set Description” for detailed information. 8025L–AVR–7/ R/W R/W R/W R ⊕ V ATmega48P/88P/168P R/W R/W R/W R SREG 11 ...

Page 12

... R15 Working R16 Registers R17 … R26 R27 R28 R29 R30 R31 Figure 6-2, each register is also assigned a data memory address, mapping them ATmega48P/88P/168P 0 Addr. 0x00 0x01 0x02 0x0D 0x0E 0x0F 0x10 0x11 0x1A X-register Low Byte 0x1B X-register High Byte ...

Page 13

... Data is pushed onto the stack Return address is pushed onto the stack with a subroutine call or Decremented by 2 interrupt Incremented by 1 Data is popped from the stack Incremented by 2 Return address is popped from the stack with return from subroutine or return from interrupt ATmega48P/88P/168P Figure 6- R26 (0x1A ...

Page 14

... Instruction Fetch 3rd Instruction Fetch 4th Instruction Fetch shows the internal timing concept for the Register File single clock cycle an ALU Single Cycle ALU Operation T1 clk CPU Total Execution Time Result Write Back ATmega48P/88P/168P SP12 SP11 SP10 SP9 SP4 SP3 ...

Page 15

... CLI instruction. The following example shows how this can be used to avoid interrupts during the timed EEPROM write sequence. 8025L–AVR–7/10 for details. ”Interrupts” on page 58 ”Boot Loader Support – Read-While-Write Self-Programming, 275. ATmega48P/88P/168P ”Memory Program- ”Interrupts” on page 58. The list also for more information. 15 ...

Page 16

... Program Counter (two bytes) is popped back from the Stack, the Stack Pointer is incremented by two, and the I-bit in SREG is set. 8025L–AVR–7/10 ; store SREG value ; disable interrupts during timed sequence ; start EEPROM write ; restore SREG value (I-bit) ; set Global Interrupt Enable ATmega48P/88P/168P 16 ...

Page 17

... The Flash memory has an endurance of at least 10,000 write/erase cycles. The ATmega48P/88P/168P Program Counter (PC) is 11/12/13 bits wide, thus addressing the 2/4/8 program memory locations. The operation of Boot Program section and associated Boot Lock bits for software protection are described in detail in on page 267 and ATmega168P” ...

Page 18

... Figure 7-1. Figure 7-2. 8025L–AVR–7/10 Program Memory Map, ATmega48P Program Memory Application Flash Section Program Memory Map, ATmega88P and ATmega168P Program Memory Application Flash Section Boot Flash Section ATmega48P/88P/168P 0x0000 0x7FF 0x0000 0x0FFF/0x1FFF 18 ...

Page 19

... SRAM Data Memory Figure 7-3 The ATmega48P/88P/168P is a complex microcontroller with more peripheral units than can be supported within the 64 locations reserved in the Opcode for the IN and OUT instructions. For the Extended I/O space from 0x60 - 0xFF in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used ...

Page 20

... Figure 7-4. 7.4 EEPROM Data Memory The ATmega48P/88P/168P contains 256/512/512 bytes of data EEPROM memory orga- nized as a separate data space, in which single bytes can be read and written. The EEPROM has an endurance of at least 100,000 write/erase cycles. The access between the EEPROM and the CPU is described in the following, specifying the EEPROM Address Registers, the EEPROM Data Register, and the EEPROM Control Register ...

Page 21

... The I/O space definition of the ATmega48P/88P/168P is shown in 395. All ATmega48P/88P/168P I/Os and peripherals are placed in the I/O space. All I/O locations may be accessed by the LD/LDS/LDD and ST/STS/STD instructions, transferring data between the 32 general purpose working registers and the I/O space. I/O Registers within the address range 0x00 - 0x1F are directly bit-accessible using the SBI and CBI instructions ...

Page 22

... Initial Value • Bits 7:6 – Reserved These bits are reserved bits in the ATmega48P/88P/168P and will always read as zero. • Bits 5, 4 – EEPM1 and EEPM0: EEPROM Programming Mode Bits The EEPROM Programming mode bit setting defines which programming action that will be trig- gered when writing EEPE ...

Page 23

... EEPROM access to fail recommended to have the Global Interrupt Flag cleared during all the steps to avoid these problems. 8025L–AVR–7/10 EEPROM Mode Bits Programming EEPM0 Time Operation 0 3.4 ms Erase and Write in one operation (Atomic Operation) 1 1.8 ms Erase Only 0 1.8 ms Write Only 1 – Reserved for future use ATmega48P/88P/168P ”Boot Loader 23 ...

Page 24

... Flash Boot Loader is present in the software. If such code is present, the EEPROM write function must also wait for any ongoing SPM command to finish. 8025L–AVR–7/10 EEPROM Programming Time Number of Calibrated RC Oscillator Cycles 26,368 ATmega48P/88P/168P Table 7-2 lists the typical pro- Typ Programming Time 3 ...

Page 25

... Start eeprom write by setting EEPE sbi EECR,EEPE ret /* Wait for completion of previous write */ while(EECR & (1<<EEPE Set up address and Data Registers */ EEAR = uiAddress; EEDR = ucData; /* Write logical one to EEMPE */ EECR |= (1<<EEMPE); /* Start eeprom write by setting EEPE */ EECR |= (1<<EEPE); ATmega48P/88P/168P 25 ...

Page 26

... Set up address register */ EEAR = uiAddress; /* Start eeprom read by writing EERE */ EECR |= (1<<EERE); /* Return data from Data Register */ return EEDR MSB R/W R/W R MSB R/W R/W R MSB R/W R/W R ATmega48P/88P/168P R/W R/W R/W R R/W R/W R/W R R/W R/W R/W R ...

Page 27

... I/O Control Unit clk ASY System Clock Prescaler Clock Multiplexer Timer/Counter External Clock Oscillator is halted, TWI address recognition in all sleep modes. I/O ATmega48P/88P/168P CPU Core RAM clk ADC clk CPU clk FLASH Reset Logic Watchdog Timer Source clock Watchdog clock Watchdog ...

Page 28

... ASY Device Clocking Options Select 1. For all fuses “1” means unprogrammed while “0” means programmed. to start oscillating and a minimum number of oscillating CC , the device issues an internal reset with a time-out delay (t CC ATmega48P/88P/168P (1) CKSEL[3:0] 1111 - 1000 0111 - 0110 0101 - 0100 0011 ...

Page 29

... Number of Watchdog Oscillator Cycles = 5.0V) Typ Time-out ( 4 before it releases the reset, and the time-out delay CC 31. Table 8-3 on page ATmega48P/88P/168P 322. = 3.0V) Number of Cycles CC 0 512 8K (8,192) Figure 8-2 on page 30. Either a quartz 30. For ceramic resonators, the capacitor val- . The ” ...

Page 30

... Fuse can be programmed in order to divide the internal frequency must be ensured that the resulting divided clock meets the frequency specification of the device. Start-up Times for the Low Power Crystal Oscillator Clock Selection Start-up Time from Power-down and Power-save 258 CK 258 ATmega48P/88P/168P XTAL2 (TOSC2) XTAL1 (TOSC1) GND (3) CKSEL[3:1] – the CKDIV8 ...

Page 31

... Recommended Range for Capacitors C1 and C2 (pF) 0 MHz frequency exceeds the specification of the device (depends on V can be programmed in order to divide the internal frequency must be ensured that the resulting divided clock meets the frequency specification of the device. ATmega48P/88P/168P Additional Delay from Reset (V = 5.0V) CKSEL0 ...

Page 32

... These options are intended for use with ceramic resonators and will ensure frequency stability at start-up. They can also be used with crystals when not operating close to the maximum fre- quency of the device, and if frequency stability at start-up is not important for the application. ATmega48P/88P/168P XTAL2 (TOSC2) XTAL1 (TOSC1) ...

Page 33

... When selecting crystals, load capasitance and crystal’s Equivalent Series Resistance, ESR must be taken into consideration. Both values are specified by the crystal vendor. ATmega48P/88P/168P oscillator is optimized for very low power consumption, and thus when selecting crystals, see 9.0 pF and 12.5 pF crystals Table 8-7 ...

Page 34

... Reserved 1. If the RSTDISBL fuse is programmed, this start-up time will be increased to 14CK + 4 ensure programming mode can be entered. The device is shipped with this option selected. 2. ATmega48P/88P/168P Recommended Usage Stable frequency at start-up for more details. ”OSCCAL – Oscillator Calibration Register” on Table 28-1 on page 294 ...

Page 35

... To run the device on an external clock, the CKSEL Fuses must be programmed Table 8-15). Crystal Oscillator Clock Frequency Frequency MHz External Clock Drive Configuration NC EXTERNAL CLOCK SIGNAL ATmega48P/88P/168P Table 8-13. CKSEL[3:0] 0011 Additional Delay from Reset (1) 14CK 14CK + 4 ms 14CK + 64 ms ...

Page 36

... System Clock Prescaler The ATmega48P/88P/168P has a system clock prescaler, and the system clock can be divided by setting the decrease the system clock frequency and the power consumption when the requirement for pro- cessing power is low ...

Page 37

... Write the Clock Prescaler Change Enable (CLKPCE) bit to one and all other bitsin CLKPR to zero. 2. Within four cycles, write the desired value to CLKPS while writing a zero to CLKPCE. Interrupts must be disabled when changing prescaler setting to make sure the write procedure is not interrupted. 8025L–AVR–7/10 ATmega48P/88P/168P 37 ...

Page 38

... R/W R/W R/W Device Specific Calibration Value Table 28-1 on page 313. The application software can write this register to change 313. Calibration outside that range is not guaranteed CLKPCE – – R 39. ATmega48P/88P/168P CAL3 CAL2 CAL1 R/W R/W R – CLKPS3 CLKPS2 CLKPS1 R R/W ...

Page 39

... The device is shipped with the CKDIV8 Fuse programmed. Table 8-17. CLKPS3 8025L–AVR–7/10 Clock Prescaler Select CLKPS2 CLKPS1 ATmega48P/88P/168P CLKPS0 Clock Division Factor 128 0 256 1 Reserved 0 Reserved 1 Reserved 0 Reserved 1 Reserved 0 Reserved 1 Reserved 39 ...

Page 40

... SLEEP. The contents of the Register File and SRAM are unaltered when the device wakes up from sleep reset occurs during sleep mode, the MCU wakes up and executes from the Reset Vector. 8025L–AVR–7/10 for more details. presents the different clock systems in the ATmega48P/88P/168P, and Oscillators ( ...

Page 41

... CPU FLASH 1. Timer/Counter2 will only keep running in asynchronous mode, see PWM and Asynchronous Operation” on page 142 ATmega48P/88P/168P Table 27-6 on page level has dropped during the sleep period. CC 45. Writing this bit to one turns off the BOD in rele- ...

Page 42

... SLEEP instruction makes the MCU enter Extended Standby mode. This mode is identical to Power-save with the exception that the Oscillator is kept running. From Extended Standby mode, the device wakes up in six clock cycles. 8025L–AVR–7/10 ATmega48P/88P/168P ”External Interrupts” on page 68 ”Clock Sources” on page 28. ...

Page 43

... Reference” on page 50 8025L–AVR–7/10 ”PRR – Power Reduction Register” on page ”Analog Comparator” on page 244 for details on the start-up time. ATmega48P/88P/168P ”Analog-to-Digital Converter” on page 248 for details on how to configure the Analog ”Brown-out Detection” on page 49 ”Internal Volt- ...

Page 44

... input pin can cause significant current even in active mode. Digital CC ”DIDR1 – Digital Input Disable Register 1” on page 247 for details. ATmega48P/88P/168P ) are stopped, the input buffers of the device will and ”DIDR0 – Digital for details on 44 ...

Page 45

... Read/Write Initial Value • Bits 7:4 – Reserved These bits are unused bits in the ATmega48P/88P/168P, and will always read as zero. • Bits 3:1 – SM[2:0]: Sleep Mode Select Bits 2, 1, and 0 These bits select between the five available sleep modes as shown in Table 9-2 ...

Page 46

... Bit 4 – Res: Reserved bit This bit is reserved in ATmega48P/88P/168P and will always read as zero. • Bit 3 – PRTIM1: Power Reduction Timer/Counter1 Writing a logic one to this bit shuts down the Timer/Counter1 module. When the Timer/Counter1 is enabled, operation will continue like before the shutdown. • ...

Page 47

... Reset Vector. For the ATmega168P, the instruction placed at the Reset Vector must be a JMP – Absolute Jump – instruction to the reset handling routine. For the ATmega48P and ATmega88P, the instruction placed at the Reset Vector must be an RJMP – Relative Jump – ...

Page 48

... Reset Characteristics” on page rise. The RESET signal is activated again, without any delay, CC decreases below the detection level POT RST RESET t TOUT RESET ATmega48P/88P/168P DATA BUS MCU Status Register (MCUSR) Delay Counters CK TIMEOUT 314. The POR is activated whenever CC 48 ...

Page 49

... RSTDISBL fuse, see Figure 10-4. External Reset During Operation 10.5 Brown-out Detection ATmega48P/88P/168P has an On-chip Brown-out Detection (BOD) circuit for monitoring the V level during operation by comparing fixed trigger level. The trigger level for the BOD CC can be selected by the BODLEVEL Fuses. The trigger level has a hysteresis to ensure spike free Brown-out Detection ...

Page 50

... Figure 10-6. Watchdog System Reset During Operation 10.7 Internal Voltage Reference ATmega48P/88P/168P features an internal bandgap reference. This reference is used for Brown-out Detection, and it can be used as an input to the Analog Comparator or the ADC. 10.7.1 Voltage Reference Enable Signals and Start-up Time The voltage reference has a start-up time that may influence the way it should be used ...

Page 51

... Possible Hardware fuse Watchdog always on (WDTON) for fail-safe mode 10.8.2 Overview ATmega48P/88P/168P has an Enhanced Watchdog Timer (WDT). The WDT is a timer counting cycles of a separate on-chip 128 kHz oscillator. The WDT gives an interrupt or a system reset when the counter reaches a given time-out value. In normal operation mode required that the system uses the WDR - Watchdog Timer Reset - instruction to restart the counter before the time-out value is reached ...

Page 52

... The following code example shows one assembly and one C function for turning off the Watch- dog Timer. The example assumes that interrupts are controlled (e.g. by disabling interrupts globally) so that no interrupts will occur during the execution of these functions. 8025L–AVR–7/10 ATmega48P/88P/168P 52 ...

Page 53

... Clear WDRF in MCUSR */ MCUSR &= ~(1<<WDRF); /* Write logical one to WDCE and WDE */ /* Keep old prescaler setting to prevent unintentional time-out */ WDTCSR |= (1<<WDCE) | (1<<WDE); /* Turn off WDT */ WDTCSR = 0x00; __enable_interrupt(); 1. See ”About Code Examples” on page 8. ATmega48P/88P/168P 53 ...

Page 54

... Finished setting new values, used 2 cycles - ; Turn on global interrupt sei ret (1) __disable_interrupt(); __watchdog_reset(); /* Start timed equence */ WDTCSR |= (1<<WDCE) | (1<<WDE); /* Set new prescaler(time-out) value = 64K cycles (~0 WDTCSR = (1<<WDE) | (1<<WDP2) | (1<<WDP0); __enable_interrupt(); 1. See ”About Code Examples” on page 8. ATmega48P/88P/168P 54 ...

Page 55

... Initial Value • Bit 7:4 – Reserved These bits are unused bits in the ATmega48P/88P/168P, and will always read as zero. • Bit 3 – WDRF: Watchdog System Reset Flag This bit is set if a Watchdog System Reset occurs. The bit is reset by a Power-on Reset writing a logic zero to the flag. • ...

Page 56

... WDP0 ATmega48P/88P/168P Action on Time-out None Interrupt Reset Interrupt, then go to System Reset Mode Reset Typical Time-out at Cycles 2K (2048) cycles 4K (4096) cycles 8K (8192) cycles 16K (16384) cycles 32K (32768) cycles 64K (65536) cycles 128K (131072) cycles 256K (262144) cycles 0.125 s 0.25 s ...

Page 57

... Table 10-2. WDP3 8025L–AVR–7/10 Watchdog Timer Prescale Select (Continued) Number of WDT Oscillator WDP2 WDP1 WDP0 512K (524288) cycles 1024K (1048576) cycles ATmega48P/88P/168P Typical Time-out at Cycles V = 5.0V CC 4.0 s 8.0 s Reserved 57 ...

Page 58

... Each Interrupt Vector occupies two instruction words in ATmega168P, and one instruction word in ATmega48P and ATmega88P. • ATmega48P does not have a separate Boot Loader Section. In ATmega88P and ATmega168P, the Reset Vector is affected by the BOOTRST fuse, and the Interrupt Vector start address is affected by the IVSEL bit in MCUCR. ...

Page 59

... Table 11-1. Reset and Interrupt Vectors in ATmega48P (Continued) Vector No. Program Address 24 0x017 25 0x018 26 0x019 The most typical and general program setup for the Reset and Interrupt Vector Addresses in ATmega48P is: Address Labels Code 0x000 0x001 0x002 0x003 0x004 0x005 0x006 0x007 0x008 ...

Page 60

... USART, Data Register Empty USART, TX USART, Tx Complete ADC ADC Conversion Complete EE READY EEPROM Ready ANALOG COMP Analog Comparator TWI 2-wire Serial Interface SPM READY Store Program Memory Ready shows reset and Interrupt Vectors placement for the various combina- ATmega48P/88P/168P ”Boot Loader Sup- 275. 60 ...

Page 61

... Main program start out SPH,r16 ldi r16, low(RAMEND) out SPL,r16 sei <instr> xxx ATmega48P/88P/168P (1) Interrupt Vectors Start Address 0x001 Boot Reset Address + 0x001 0x001 Boot Reset Address + 0x001 Table 26-7 on page 287. For the BOOTRST Fuse “1” Comments ...

Page 62

... RESET rjmp EXT_INT0 rjmp EXT_INT1 ... ... rjmp SPM_RDY RESET: ldi r16,high(RAMEND); Main program start ATmega48P/88P/168P Comments ; Set Stack Pointer to top of RAM ; Enable interrupts ; IRQ0 Handler ; IRQ1 Handler ; ; Store Program Memory Ready Handler ; IRQ0 Handler ; IRQ1 Handler ; ; Store Program Memory Ready Handler ...

Page 63

... USART, UDRE USART, Data Register Empty USART, TX USART, Tx Complete ADC ADC Conversion Complete EE READY EEPROM Ready ANALOG COMP Analog Comparator TWI 2-wire Serial Interface SPM READY Store Program Memory Ready ATmega48P/88P/168P ; Set Stack Pointer to top of RAM ; Enable interrupts ”Boot Loader Sup- 275. 63 ...

Page 64

... EE_RDY jmp ANA_COMP jmp TWI jmp SPM_RDY ldi r16, high(RAMEND); Main program start ATmega48P/88P/168P (1) Interrupt Vectors Start Address 0x002 Boot Reset Address + 0x0002 0x002 Boot Reset Address + 0x0002 Table 26-7 on page 287. For the BOOTRST Fuse “1” Comments ; Reset Handler ...

Page 65

... RESET: ldi r16,high(RAMEND); Main program start out SPH,r16 ldi r16,low(RAMEND) out SPL,r16 sei <instr> xxx ATmega48P/88P/168P ; Set Stack Pointer to top of RAM ; Enable interrupts Comments ; Set Stack Pointer to top of RAM ; Enable interrupts ; IRQ0 Handler ; IRQ1 Handler ; ; Store Program Memory Ready Handler ; IRQ0 Handler ...

Page 66

... IVCE is set, and they remain disabled until after the instruction following the write to IVSEL. If IVSEL is not written, interrupts remain disabled for four cycles. The I-bit in the Status Register is unaffected by the automatic disabling. Note: This bit is not available in ATmega48P. 8025L–AVR–7/10 jmp RESET ...

Page 67

... IVSEL description above. See Code Example below. Assembly Code Example Move_interrupts: C Code Example void Move_interrupts(void This bit is not available in ATmega48P. 8025L–AVR–7/10 ; Enable change of Interrupt Vectors ldi r16, (1<<IVCE) out MCUCR, r16 ; Move interrupts to Boot Flash section ldi r16, (1<<IVSEL) ...

Page 68

... Figure 12-1. Timing of pin change interrupts 8025L–AVR–7/10 27. Low level interrupt on INT0 and INT1 is detected asynchro- 27. pin_lat pcint_in_(0) PCINT( pin_sync LE clk PCINT(0) in PCMSK(x) clk PCINT(0) pin_lat pin_sync pcint_in_(0) pcint_syn pcint_setflag PCIF ATmega48P/88P/168P ”Clock Systems Figure 12-1. 0 pcint_syn pcint_setflag PCIF x clk 68 ...

Page 69

... Initial Value • Bit 7:4 – Reserved These bits are unused bits in the ATmega48P/88P/168P, and will always read as zero. • Bit 3, 2 – ISC11, ISC10: Interrupt Sense Control 1 Bit 1 and Bit 0 The External Interrupt 1 is activated by the external pin INT1 if the SREG I-flag and the corre- sponding interrupt mask are set ...

Page 70

... Initial Value • Bit 7:2 – Reserved These bits are unused bits in the ATmega48P/88P/168P, and will always read as zero. • Bit 1 – INT1: External Interrupt Request 1 Enable When the INT1 bit is set (one) and the I-bit in the Status Register (SREG) is set (one), the exter- nal pin interrupt is enabled ...

Page 71

... Initial Value • Bit 7:3 – Reserved These bits are unused bits in the ATmega48P/88P/168P, and will always read as zero. • Bit 2 – PCIE2: Pin Change Interrupt Enable 2 When the PCIE2 bit is set (one) and the I-bit in the Status Register (SREG) is set (one), pin change interrupt 2 is enabled ...

Page 72

... Initial Value • Bit 7 – Reserved Bit This bit is an unused bit in the ATmega48P/88P/168P, and will always read as zero. • Bit 6:0 – PCINT[14:8]: Pin Change Enable Mask 14..8 Each PCINT[14:8]-bit selects whether pin change interrupt is enabled on the corresponding I/O pin ...

Page 73

... Ground as indicated in CC for a complete list of parameters. Pxn C pin ”Register Description” on page 78. Refer to the individual module sections for a full description of the alter- ATmega48P/88P/168P Figure 13-1. Refer to ”Electrical Char Logic See Figure "General Digital I/O" for Details 90. ” ...

Page 74

... WRx, WPx, WDx, RRx, RPx, and RDx are common to all pins within the same port. clk SLEEP, and PUD are common to all ports. 90, the DDxn bits are accessed at the DDRx I/O address, the PORTxn bits ATmega48P/88P/168P Figure 13-2 shows a func- PUD ...

Page 75

... Input 1 1 Input 0 X Output 1 X Output Figure 13-2, the PINxn Register bit and the preceding latch con- pd,max ATmega48P/88P/168P Pull-up Comment No Tri-state (Hi-Z) Yes Pxn will source current if ext. pulled low. No Tri-state (Hi-Z) No Output Low (Sink) No Output High (Source) Figure 13-3 ...

Page 76

... SYNC LATCH PINxn r17 Figure 13-4. The out instruction sets the “SYNC LATCH” signal at the positive edge of SYSTEM CLK r16 out PORTx, r16 SYNC LATCH PINxn r17 ATmega48P/88P/168P XXX in r17, PINx 0x00 t pd, max t pd, min 0xFF nop in r17, PINx ...

Page 77

... Figure 13-2, the digital input signal can be clamped to ground at the input of the ”Alternate Port Functions” on page ATmega48P/88P/168P /2. CC 78. 77 ...

Page 78

... Pxn, PORT TOGGLE OVERRIDE ENABLE 1. WRx, WPx, WDx, RRx, RPx, and RDx are common to all pins within the same port. clk SLEEP, and PUD are common to all ports. All other signals are unique for each pin. ATmega48P/88P/168P Figure 13-2 on page 74 PUD ...

Page 79

... Unless the Digital Input is used as a clock source, the module with the alternate function will use its own synchronizer. This is the Analog Input/output to/from alternate functions. The Analog signal is connected directly to the pad, and can be used bi- Input/Output directionally. ATmega48P/88P/168P Fig- 79 ...

Page 80

... SS (SPI Bus Master Slave select) OC1B (Timer/Counter1 Output Compare Match B Output) PCINT2 (Pin Change Interrupt 2) OC1A (Timer/Counter1 Output Compare Match A Output) PCINT1 (Pin Change Interrupt 1) ICP1 (Timer/Counter1 Input Capture Input) CLKO (Divided System Clock Output) PCINT0 (Pin Change Interrupt 0) ATmega48P/88P/168P Table 13- ...

Page 81

... PCINT2: Pin Change Interrupt source 2. The PB2 pin can serve as an external interrupt source. • OC1A/PCINT1 – Port B, Bit 1 OC1A, Output Compare Match output: The PB1 pin can serve as an external output for the Timer/Counter1 Compare Match A. The PB1 pin has to be configured as an output (DDB1 set 8025L–AVR–7/10 ATmega48P/88P/168P 81 ...

Page 82

... AS2 PCINT7 INPUT PCINT6 INPUT Oscillator/Clock Oscillator Output Input 1. INTRC means that one of the internal RC Oscillators are selected (by the CKSEL fuses), EXTCK means that external clock is selected (by the CKSEL fuses) ATmega48P/88P/168P PB5/SCK/ PB4/MISO/ (1) PCINT5 PCINT4 SPE • MSTR SPE • MSTR PORTB5 • ...

Page 83

... ADC3 (ADC Input Channel 3) PC3 PCINT11 (Pin Change Interrupt 11) ADC2 (ADC Input Channel 2) PC2 PCINT10 (Pin Change Interrupt 10) ADC1 (ADC Input Channel 1) PC1 PCINT9 (Pin Change Interrupt 9) ADC0 (ADC Input Channel 0) PC0 PCINT8 (Pin Change Interrupt 8) ATmega48P/88P/168P PB1/OC1A/ PB0/ICP1/ PCINT1 PCINT0 ...

Page 84

... PCINT11: Pin Change Interrupt source 11. The PC3 pin can serve as an external interrupt source. • ADC2/PCINT10 – Port C, Bit 2 PC2 can also be used as ADC input Channel 2. Note that ADC input channel 2 uses analog power. PCINT10: Pin Change Interrupt source 10. The PC2 pin can serve as an external interrupt source. 8025L–AVR–7/10 ATmega48P/88P/168P 84 ...

Page 85

... When enabled, the 2-wire Serial Interface enables slew-rate controls on the output pins PC4 and PC5. This is not shown in the figure. In addition, spike filters are connected between the AIO outputs shown in the port figure and the digital logic of the TWI module. ATmega48P/88P/168P (1) PC4/SDA/ADC4/PCINT12 TWEN PORTC4 • ...

Page 86

... OC2B (Timer/Counter2 Output Compare Match B Output) PCINT19 (Pin Change Interrupt 19) INT0 (External Interrupt 0 Input) PD2 PCINT18 (Pin Change Interrupt 18) TXD (USART Output Pin) PD1 PCINT17 (Pin Change Interrupt 17) RXD (USART Input Pin) PD0 PCINT16 (Pin Change Interrupt 16) ATmega48P/88P/168P PC1/ADC1/ PC0/ADC0/ PCINT9 PCINT8 ...

Page 87

... Timer/Counter0 Compare Match B. The PD3 pin has to be configured as an output (DDD3 set (one)) to serve this function. The OC2B pin is also the output pin for the PWM mode timer function. PCINT19: Pin Change Interrupt source 19. The PD3 pin can serve as an external interrupt source. 8025L–AVR–7/10 ATmega48P/88P/168P 87 ...

Page 88

... OC0A/PCINT22 OC0A ENABLE 0 OC0A PCINT23 • PCIE2 PCINT22 • PCIE2 1 1 PCINT23 INPUT PCINT22 INPUT AIN1 INPUT AIN0 INPUT ATmega48P/88P/168P PD5/T1/OC0B/ PD4/XCK/ PCINT21 T0/PCINT20 OC0B ENABLE UMSEL OC0B XCK OUTPUT PCINT21 • PCIE2 PCINT20 • PCIE2 1 1 PCINT20 INPUT PCINT21 INPUT ...

Page 89

... OC2B ENABLE 0 OC2B 0 INT1 ENABLE + INT0 ENABLE + PCINT19 • PCIE2 PCINT18 • PCIE1 1 1 PCINT19 INPUT PCINT18 INPUT INT1 INPUT INT0 INPUT – – ATmega48P/88P/168P PD1/TXD/ PD0/RXD/ PCINT17 PCINT16 TXEN RXEN 0 PORTD0 • PUD TXEN RXEN 1 0 TXEN 0 TXD 0 PCINT17 • PCIE2 PCINT16 • ...

Page 90

... PORTC6 PORTC5 PORTC4 R R/W R/W R – DDC6 DDC5 DDC4 R R/W R/W R – PINC6 PINC5 PINC4 N/A N/A N/A ATmega48P/88P/168P – – IVSEL IVCE R R R/W R PORTB3 PORTB2 PORTB1 PORTB0 R/W R/W R/W R DDB3 DDB2 DDB1 DDB0 R/W R/W R/W R/W ...

Page 91

... PORTD7 PORTD6 PORTD5 PORTD4 R/W R/W R/W R DDD7 DDD6 DDD5 DDD4 R/W R/W R/W R PIND7 PIND6 PIND5 PIND4 N/A N/A N/A N/A ATmega48P/88P/168P PORTD3 PORTD2 PORTD1 PORTD0 R/W R/W R/W R DDD3 DDD2 DDD1 DDD0 R/W R/W R/W R PIND3 PIND2 PIND1 PIND0 ...

Page 92

... Registers, including I/O bits and I/O pins, are shown in bold. The device-specific I/O Register and bit locations are listed in the The PRTIM0 bit in enable Timer/Counter0 module. 8025L–AVR–7/10 ”Pinout ATmega48P/88P/168P” on page ”Register Description” on page ”Minimizing Power Consumption” on page 43 ATmega48P/88P/168P Figure 14-1 ...

Page 93

... The counter reaches the TOP when it becomes equal to the highest value in the count sequence. The TOP value can be assigned to be the fixed value 0xFF (MAX) or the value stored in the OCR0A Register. The assignment is depen- dent on the mode of operation. ATmega48P/88P/168P TOVn (Int.Req.) Clock Select ...

Page 94

... Signalize that TCNT0 has reached minimum value (zero). ). clk can be generated from an external or internal clock source present or not. A CPU write overrides (has priority over) all counter clear or T0 ATmega48P/88P/168P for details. The compare match event will also set the 139. TOVn (Int.Req.) Clock Select Edge ...

Page 95

... PWM pulses, thereby making the output glitch-free. 8025L–AVR–7/10 97. (”Modes of Operation” on page shows a block diagram of the Output Compare unit. DATA BUS OCRnx = (8-bit Comparator ) top bottom Waveform Generator FOCn WGMn1:0 ATmega48P/88P/168P 97). TCNTn OCFnx (Int.Req.) OCnx COMnx1:0 ”Modes of 95 ...

Page 96

... PORT) that are affected by the COM0x1:0 bits are shown. When referring to the OC0x state, the reference is for the internal OC0x Register, not the OC0x pin system reset occur, the OC0x Register is reset to “0”. 8025L–AVR–7/10 ATmega48P/88P/168P Figure 14-4 shows a simplified 96 ...

Page 97

... COMnx1 Waveform COMnx0 D Generator FOCn D PORT D clk I/O See Section “14.9” on page 104. Table 14-2 on page 96.). ”Timer/Counter Timing Diagrams” on page ATmega48P/88P/168P Q 1 OCnx Pin OCnx DDR 104. For fast PWM mode, refer to Table 14-4 on page 105. Table 14-3 on 102. ...

Page 98

... For generating a waveform output in CTC mode, the OC0A output can be set to toggle its logical level on each compare match by setting the Compare Output mode bits to toggle mode (COM0A1:0 = 1). The OC0A value will not be visible on the port pin unless the data direction for 8025L–AVR–7/10 ATmega48P/88P/168P Figure 1 2 ...

Page 99

... OCnx Figure 14-6. The TCNT0 value is in the timing diagram shown as a his ATmega48P/88P/168P ) OCRnx OCRnx Interrupt Flag Set OCRnx Update and TOVn Interrupt Flag Set (COMnx1 (COMnx1 OC0 99 ...

Page 100

... TCNT0 slopes represent compare matches between OCR0x and TCNT0. 8025L–AVR–7/10 Table 14-6 on page f OCnxPWM 14-7. The TCNT0 value is in the timing diagram shown as a histogram for illustrating ATmega48P/88P/168P 105). The actual OC0x value will only be visible on f clk_I/O = ----------------- - ⋅ ...

Page 101

... Compare Match. The point of this transition is to guarantee symmetry around BOT- TOM. There are two cases that give a transition without Compare Match. • OCRnx changes its value from MAX, like in OCn pin value is the same as the result of a down-counting Compare Match. To ensure 8025L–AVR–7/10 ATmega48P/88P/168P Table 14-7 on page 106) ...

Page 102

... I/O Tn /1) I/O MAX - 1 shows the same timing data, but with the prescaler enabled. I/O Tn /8) I/O MAX - 1 shows the setting of OCF0B in all modes and OCF0A in all modes except CTC ATmega48P/88P/168P ) is therefore shown MAX BOTTOM /8) clk_I/O MAX BOTTOM BOTTOM + 1 BOTTOM + 1 102 ...

Page 103

... OCRnx OCFnx 8025L–AVR–7/10 I/O Tn /8) I/O OCRnx - 1 shows the setting of OCF0A and the clearing of TCNT0 in CTC mode and fast caler (f /8) clk_I/O I/O Tn /8) I/O TOP - 1 ATmega48P/88P/168P OCRnx OCRnx + 1 OCRnx Value TOP BOTTOM TOP /8) clk_I/O OCRnx + 2 BOTTOM + 1 103 ...

Page 104

... Set OC0A on Compare Match, clear OC0A at BOTTOM, 1 (inverting mode special case occurs when OCR0A equals TOP and COM0A1 is set. In this case, the Com- pare Match is ignored, but the set or clear is done at BOTTOM. See page 99 for more details. ATmega48P/88P/168P COM0B0 – – ...

Page 105

... A special case occurs when OCR0B equals TOP and COM0B1 is set. In this case, the Com- pare Match is ignored, but the set or clear is done at TOP. See for more details. ATmega48P/88P/168P (1) ”Phase Correct PWM Mode” on (1) ”Fast PWM Mode” on page 99 ...

Page 106

... Note: • Bits 3, 2 – Reserved These bits are reserved bits in the ATmega48P/88P/168P and will always read as zero. • Bits 1:0 – WGM01:0: Waveform Generation Mode Combined with the WGM02 bit found in the TCCR0B Register, these bits control the counting sequence of the counter, the source for maximum (TOP) counter value, and what type of wave- ...

Page 107

... OCR0B as TOP. The FOC0B bit is always read as zero. • Bits 5:4 – Reserved These bits are reserved bits in the ATmega48P/88P/168P and will always read as zero. • Bit 3 – WGM02: Waveform Generation Mode See the description in the • Bits 2:0 – CS02:0: Clock Select The three Clock Select bits select the clock source to be used by the Timer/Counter. 8025L– ...

Page 108

... I External clock source on T0 pin. Clock on falling edge External clock source on T0 pin. Clock on rising edge R/W R/W R/W R R/W R/W R/W R R/W R/W R/W R ATmega48P/88P/168P TCNT0[7:0] R/W R/W R OCR0A[7:0] R/W R/W R OCR0B[7:0] R/W R/W R TCNT0 R/W ...

Page 109

... Initial Value • Bits 7:3 – Reserved These bits are reserved bits in the ATmega48P/88P/168P and will always read as zero. • Bit 2 – OCIE0B: Timer/Counter Output Compare Match B Interrupt Enable When the OCIE0B bit is written to one, and the I-bit in the Status Register is set, the Timer/Counter Compare Match B interrupt is enabled ...

Page 110

... When the SREG I-bit, TOIE0 (Timer/Counter0 Overflow Interrupt Enable), and TOV0 are set, the Timer/Counter0 Overflow interrupt is executed. The setting of this flag is dependent of the WGM02:0 bit setting. Refer to Generation Mode Bit Description” on page 8025L–AVR–7/10 ATmega48P/88P/168P Table 106. 14-8, ”Waveform ...

Page 111

... Registers, including I/O bits and I/O pins, are shown in bold. The device-specific I/O Register and bit locations are listed in the The PRTIM1 bit in enable Timer/Counter1 module. 8025L–AVR–7/10 ”Pinout ATmega48P/88P/168P” on page ”Register Description” on page ”PRR – Power Reduction Register” on page 46 ATmega48P/88P/168P Figure 15-1 ...

Page 112

... Count Clear Control Logic Direction Timer/Counter TCNTn = OCRnA = OCRnB ICRn TCCRnA Table 13-3 on page 80 1. Refer to Figure 1-1 on page 2, Timer/Counter1 pin placement and description. ATmega48P/88P/168P (1) TOVn (Int.Req.) Clock Select clk Tn Edge Detector TOP BOTTOM ( From Prescaler ) = = 0 OCnA (Int.Req.) Waveform ...

Page 113

... The counter reaches the TOP when it becomes equal to the highest value in the count sequence. The TOP value can be assigned to be one of the fixed values: 0x00FF, 0x01FF, or 0x03FF the value stored in the OCR1A or ICR1 Register. The assignment is dependent of the mode of operation. ATmega48P/88P/168P 113 ...

Page 114

... For I/O Registers located in extended I/O map, “IN”, “OUT”, “SBIS”, “SBIC”, “CBI”, and “SBI” instructions must be replaced with instructions that allow access to extended I/O. Typically “LDS” and “STS” combined with “SBRS”, “SBRC”, “SBR”, and “CBR”. ATmega48P/88P/168P 114 ...

Page 115

... For I/O Registers located in extended I/O map, “IN”, “OUT”, “SBIS”, “SBIC”, “CBI”, and “SBI” instructions must be replaced with instructions that allow access to extended I/O. Typically “LDS” and “STS” combined with “SBRS”, “SBRC”, “SBR”, and “CBR”. ATmega48P/88P/168P 115 ...

Page 116

... For I/O Registers located in extended I/O map, “IN”, “OUT”, “SBIS”, “SBIC”, “CBI”, and “SBI” instructions must be replaced with instructions that allow access to extended I/O. Typically “LDS” and “STS” combined with “SBRS”, “SBRC”, “SBR”, and “CBR”. ”Timer/Counter0 and Timer/Counter1 Prescalers” on page ATmega48P/88P/168P 139. 116 ...

Page 117

... Signalize that TCNT1 has reached minimum value (zero). ). The clk can be generated from an external or internal clock source present or not. A CPU write overrides (has priority over) all counter clear ”Modes of Operation” on page ATmega48P/88P/168P TOVn (Int.Req.) Clock Select Edge Detector clk Tn Control Logic ( From Prescaler ) TOP BOTTOM 123 ...

Page 118

... ICR1 Register for defining the counter’s TOP value. In these cases the Waveform Genera- 8025L–AVR–7/10 DATA BUS TEMP (8-bit) ICRnH (8-bit) ICRnL (8-bit) ICRn (16-bit Register) WRITE ACO* ACIC* Analog Comparator ICPn ATmega48P/88P/168P Figure 15-3. The elements of (8-bit) TCNTnH (8-bit) TCNTnL (8-bit) TCNTn (16-bit Counter) ICNC ICES Noise Edge ICFn (Int.Req.) Canceler ...

Page 119

... Changing the edge sensing must be done as early as possible after the ICR1 Register has been read. After a change of the edge, the Input Capture Flag (ICF1) must be 8025L–AVR–7/10 113. ATmega48P/88P/168P ”Accessing 16-bit Registers” (Figure 16-1 on page 139). The edge detector is also ...

Page 120

... Output Compare unit. The small “n” in the register and DATA BUS TEMP (8-bit) OCRnxH Buf. (8-bit) OCRnxL Buf. (8-bit) OCRnx Buffer (16-bit Register) OCRnxH (8-bit) OCRnxL (8-bit) OCRnx (16-bit Register) TOP BOTTOM ATmega48P/88P/168P 123.) (8-bit) TCNTnH (8-bit) TCNTnL (8-bit) TCNTn (16-bit Counter) = (16-bit Comparator ) OCFnx (Int.Req.) Waveform Generator WGMn3:0 ...

Page 121

... Normal mode. The OC1x Register keeps its value even when changing between Waveform Generation modes. Be aware that the COM1x1:0 bits are not double buffered together with the compare value. Changing the COM1x1:0 bits will take effect immediately. 8025L–AVR–7/10 113. ATmega48P/88P/168P ”Accessing 16-bit Registers” 121 ...

Page 122

... The Waveform Generator uses the COM1x1:0 bits differently in normal, CTC, and PWM modes. For all modes, setting the COM1x1 tells the Waveform Generator that no action on the OC1x Register performed on the next compare match. For compare output actions in the 8025L–AVR–7/10 Waveform Generator I/O See Section “15.11” on page 132. ATmega48P/88P/168P Figure 15 OCnx 0 D ...

Page 123

... The timing diagram for the CTC mode is shown in increases until a compare match occurs with either OCR1A or ICR1, and then counter (TCNT1) is cleared. 8025L–AVR–7/10 ATmega48P/88P/168P Table 15-1 on page 132. For fast PWM mode refer to 122.) ”Timer/Counter Timing Diagrams” on page ...

Page 124

... High frequency allows physically small sized external components (coils, capaci- tors), hence reduces total system cost. 8025L–AVR–7/ when OCR1A is set to zero (0x0000). The waveform frequency clk_I -------------------------------------------------- - ⋅ OCnA 2 N ATmega48P/88P/168P OCnA Interrupt Flag Set or ICFn Interrupt Flag Set (Interrupt on TOP) (COMnA1 clk_I/O ⋅ OCRnA 124 ...

Page 125

... The OCR1A Register however, is double buffered. This feature allows the OCR1A I/O location 8025L–AVR–7/10 ( log TOP R = ---------------------------------- - FPWM log ATmega48P/88P/168P ) Figure 15-7. The figure OCRnx/TOP Update and TOVn Interrupt Flag Set and OCnA Interrupt Flag Set or ICFn Interrupt Flag Set (Interrupt on TOP) (COMnx1 (COMnx1 ...

Page 126

... However, due to the symmetric feature of the dual-slope PWM modes, these modes are preferred for motor control applications. The PWM resolution for the phase correct PWM mode can be fixed to 8-, 9-, or 10-bit, or defined by either ICR1 or OCR1A. The minimum resolution allowed is 2-bit (ICR1 or OCR1A set to 8025L–AVR–7/10 ATmega48P/88P/168P Table on page f clk_I/O f ...

Page 127

... TOP actively while the Timer/Counter is running in the phase correct mode can result in an unsymmetrical output. The reason for this can be found in the time of update of the OCR1x Reg- ister. Since the OCR1x update occurs at TOP, the PWM period starts and ends at TOP. This 8025L–AVR–7/10 ATmega48P/88P/168P ( ) log ...

Page 128

... Figure The PWM resolution for the phase and frequency correct PWM mode can be defined by either ICR1 or OCR1A. The minimum resolution allowed is 2-bit (ICR1 or OCR1A set to 0x0003), and 8025L–AVR–7/10 f OCnxPCPWM 15-9). ATmega48P/88P/168P Table on page f clk_I/O = --------------------------- - ⋅ ⋅ TOP 133). The ...

Page 129

... R = ---------------------------------- - PFCPWM Figure 15-9. The figure shows phase and frequency correct shows the output generated is, in contrast to the phase correct mode, symmetri- ATmega48P/88P/168P ( ) + 1 TOP log OCnA Interrupt Flag Set or ICFn Interrupt Flag Set (Interrupt on TOP) OCRnx/TOP Updateand TOVn Interrupt Flag Set ...

Page 130

... OCnxPFCPWM Figure 15-10 clk I/O clk Tn (clk /1) I/O TCNTn OCRnx - 1 OCRnx OCFnx shows the same timing data, but with the prescaler enabled. ATmega48P/88P/168P f clk_I/O = --------------------------- - ⋅ ⋅ TOP ) is therefore shown shows a timing diagram for the setting of OCF1x. OCRnx OCRnx + 1 OCRnx + 2 OCRnx Value ...

Page 131

... I/O clk Tn (clk /1) I/O TCNTn TOP - 1 (CTC and FPWM) TCNTn TOP - 1 TOVn (FPWM) and ICFn (if used as TOP) OCRnx Old OCRnx Value (Update at TOP) ATmega48P/88P/168P OCRnx OCRnx + 1 OCRnx Value TOP BOTTOM TOP TOP - 1 New OCRnx Value /8) clk_I/O OCRnx + 2 BOTTOM + 1 TOP - 2 131 ...

Page 132

... OCRnx Old OCRnx Value (Update at TOP COM1A1 COM1A0 COM1B1 R/W R/W R Table 15-1 Compare Output Mode, non-PWM COM1A0/COM1B0 ATmega48P/88P/168P /8) clk_I/O TOP BOTTOM TOP TOP - 1 New OCRnx Value COM1B0 – – WGM11 R R shows the COM1x1:0 bit functionality when the Description Normal port operation, OC1A/OC1B disconnected. ...

Page 133

... A special case occurs when OCR1A/OCR1B equals TOP and COM1A1/COM1B1 is set. Section “15.9.4” on page 126. for more details. Table 15-4. Modes of operation supported by the Timer/Counter ATmega48P/88P/168P (1) Description Normal port operation, OC1A/OC1B disconnected. WGM13 15: Toggle OC1A on Compare Match, OC1B disconnected (normal port operation). ...

Page 134

... CTC 0 1 (Reserved Fast PWM 1 1 Fast PWM ICNC1 ICES1 – WGM13 R/W R ATmega48P/88P/168P Update of x TOP OCR1 0xFFFF Immediate 0x00FF TOP 0x01FF TOP 0x03FF TOP OCR1A Immediate 0x00FF BOTTOM 0x01FF BOTTOM 0x03FF BOTTOM ICR1 BOTTOM OCR1A BOTTOM ICR1 ...

Page 135

... I clk /256 (From prescaler) I clk /1024 (From prescaler) I External clock source on T1 pin. Clock on falling edge External clock source on T1 pin. Clock on rising edge FOC1A FOC1B – R/W R ATmega48P/88P/168P – – – – Figure 0 – TCCR1C R 0 135 ...

Page 136

... TCNT1[15:8] TCNT1[7:0] R/W R/W R/W R OCR1A[15:8] OCR1A[7:0] R/W R/W R/W R OCR1B[15:8] OCR1B[7:0] R/W R/W R/W R See Section “15.3” on page 113. ATmega48P/88P/168P R/W R/W R/W R See Section “15.3” R/W R/W R/W R R/W R/W R/W R TCNT1H TCNT1L OCR1AH OCR1AL OCR1BH OCR1BL ...

Page 137

... Initial Value • Bit 7, 6 – Reserved These bits are unused bits in the ATmega48P/88P/168P, and will always read as zero. • Bit 5 – ICIE1: Timer/Counter1, Input Capture Interrupt Enable When this bit is written to one, and the I-flag in the Status Register is set (interrupts globally enabled), the Timer/Counter1 Input Capture interrupt is enabled. The corresponding Interrupt Vector (see “ ...

Page 138

... Initial Value • Bit 7, 6 – Reserved These bits are unused bits in the ATmega48P/88P/168P, and will always read as zero. • Bit 5 – ICF1: Timer/Counter1, Input Capture Flag This flag is set when a capture event occurs on the ICP1 pin. When the Input Capture Register (ICR1) is set by the WGM13 used as the TOP value, the ICF1 Flag is set when the coun- ter reaches the TOP value ...

Page 139

... Alternatively, one of four taps from the prescaler can be used as a CLK_I/O ). The T1/T0 pin is sampled once every system clock cycle by the pin synchronization T0 /clk clk I/O Synchronization ATmega48P/88P/168P and ”16-bit Timer/Counter1 with PWM” on page /8, f /64, f CLK_I/O CLK_I/O pulse for each positive (CSn2 negative Edge Detector /256, or ...

Page 140

... Figure 16-2. Prescaler for Timer/Counter0 and Timer/Counter1 PSRSYNC Note: 8025L–AVR–7/10 < f /2) given a 50/50% duty cycle. Since the edge detector uses ExtClk clk_I/O clk I/O T0 Synchronization T1 Synchronization clk 1. The synchronization logic on the input pins ( ATmega48P/88P/168P (1) Clear T1 T1/T0) is shown in Figure 16-1. /2.5. clk_I/O clk T0 140 ...

Page 141

... TSM bit is set. Note that Timer/Counter1 and Timer/Counter0 share the same prescaler and a reset of this prescaler will affect both timers. 8025L–AVR–7/ TSM – – – R ATmega48P/88P/168P – – PSRASY PSRSYNC R R R/W R GTCCR 141 ...

Page 142

... I/O bits and I/O pins, are shown in bold. The device-specific I/O Register and bit loca- tions are listed in the The PRTIM2 bit in enable Timer/Counter2 module. Figure 17-1. 8-bit Timer/Counter Block Diagram 8025L–AVR–7/10 ”Pinout ATmega48P/88P/168P” on page ”Register Description” on page ”Minimizing Power Consumption” on page 43 Count Clear Control Logic ...

Page 143

... MCU clock, clk T2 154. shows a block diagram of the counter and its surrounding environment. ATmega48P/88P/168P for details. The compare match event will also set the 162. For details on clock sources and prescaler, see . When the AS2 I/O ” ...

Page 144

... Signalizes that TCNT2 has reached minimum value (zero). ). clk can be generated from an external or internal clock source present or not. A CPU write overrides (has priority over) all counter clear or T2 147. shows a block diagram of the Output Compare unit. ATmega48P/88P/168P TOVn (Int.Req.) T/C clk Tn Oscillator Prescaler clk top in the following ...

Page 145

... OCR2x value, the compare match will be missed, resulting in incorrect waveform generation. Similarly, do not write the TCNT2 value equal to BOTTOM when the counter is downcounting. 8025L–AVR–7/10 DATA BUS OCRnx = (8-bit Comparator ) top bottom Waveform Generator FOCn WGMn1:0 ATmega48P/88P/168P TCNTn OCFnx (Int.Req.) OCnx COMnX1:0 145 ...

Page 146

... The design of the Output Compare pin logic allows initialization of the OC2x state before the out- put is enabled. Note that some COM2x1:0 bit settings are reserved for certain modes of operation. 8025L–AVR–7/10 Waveform Generator clk I/O See Section “17.11” on page 156. ATmega48P/88P/168P Figure 17-4 shows a simplified OCnx 0 D ...

Page 147

... The timing diagram for the CTC mode is shown in increases until a compare match occurs between TCNT2 and OCR2A, and then counter (TCNT2) is cleared. 8025L–AVR–7/10 ATmega48P/88P/168P Table 17-5 on page 157. For fast PWM mode, refer to Table 17-7 on page 146.). ...

Page 148

... This high frequency makes the fast PWM mode well suited for power regulation, rectification, and DAC applications. High frequency allows physically small sized external components (coils, capacitors), and therefore reduces total system cost. 8025L–AVR–7/10 ATmega48P/88P/168P ...

Page 149

... Figure 17-6. The TCNT2 value is in the timing diagram shown as a his Table 17-3 on page ----------------- - OCnxPWM N 256 ATmega48P/88P/168P OCRnx Interrupt Flag Set OCRnx Update and TOVn Interrupt Flag Set (COMnx1 (COMnx1 156). The actual OC2x value will only clk_I/O ⋅ 149 ...

Page 150

... In phase correct PWM mode, the compare unit allows generation of PWM waveforms on the OC2x pin. Setting the COM2x1:0 bits to two will produce a non-inverted PWM. An inverted PWM 8025L–AVR–7/10 17-7. The TCNT2 value is in the timing diagram shown as a histogram for illustrating 1 ATmega48P/88P/168P = f /2 when OCR2A is set to zero. This fea- oc2 clk_I/O ...

Page 151

... OCnxPCPWM Figure 17-7 contains timing data for basic Timer/Counter operation. The figure shows the I/O Tn /1) I/O MAX - 1 shows the same timing data, but with the prescaler enabled. ATmega48P/88P/168P Table 17-4 on page 157). The actual OC2x f clk_I/O = ----------------- - ⋅ N 510 OCnx has a transition from high to low even though Figure 17-7 ...

Page 152

... OCF2A in all modes except CTC mode. I/O Tn /8) I/O OCRnx - 1 shows the setting of OCF2A and the clearing of TCNT2 in CTC mode. caler (f /8) clk_I/O I/O Tn /8) I/O TOP - 1 TOP ATmega48P/88P/168P /8) clk_I/O MAX BOTTOM OCRnx OCRnx + 1 OCRnx Value BOTTOM BOTTOM + 1 TOP BOTTOM + 1 /8) clk_I/O OCRnx + 2 152 ...

Page 153

... The contents of all Timer/Counter2 Registers must be considered lost after a wake-up from Power-down or Standby mode due to unstable clock signal upon start-up, no matter whether the Oscillator is in use or a clock signal is applied to the TOSC1 pin. 8025L–AVR–7/10 Enable interrupts, if needed. ATmega48P/88P/168P 153 ...

Page 154

... TCNT2 will read as the previous value (before entering sleep) clk I/O clk T2S Clear TOSC1 AS2 CS20 CS21 CS22 . By setting the AS2 bit in ASSR, Timer/Counter2 is asynchronously IO ATmega48P/88P/168P 10-BIT T/C PRESCALER 0 TIMER/COUNTER2 CLOCK SOURCE clk T2 . clk is by default connected to the main T2S T2S 154 ...

Page 155

... T2S Setting the PSRASY bit in GTCCR resets the prescaler. This allows the user to operate with a predictable prescaler. 8025L–AVR–7/10 /256, and clk /1024. Additionally, clk T2S T2S ATmega48P/88P/168P /8, clk /32, clk T2S T2S as well as 0 (stop) may be selected. T2S /64, T2S ...

Page 156

... Set OC2A on Compare Match, clear OC2A at BOTTOM, 1 (inverting mode special case occurs when OCR2A equals TOP and COM2A1 is set. In this case, the Com- pare Match is ignored, but the set or clear is done at BOTTOM. See page 148 for more details. ATmega48P/88P/168P COM2B0 – ...

Page 157

... COM2B1:0 bit functionality when the WGM22:0 bits are set to fast PWM Compare Output Mode, Fast PWM Mode COM2B0 Description 0 Normal port operation, OC2B disconnected. 1 Reserved Clear OC2B on Compare Match, set OC2B at BOTTOM, 0 (non-inverting mode). Set OC2B on Compare Match, clear OC2B at BOTTOM, 1 (inverting mode). ATmega48P/88P/168P (1) ”Phase Correct PWM Mode” on (1) 157 ...

Page 158

... Note: • Bits 3, 2 – Reserved These bits are reserved bits in the ATmega48P/88P/168P and will always read as zero. • Bits 1:0 – WGM21:0: Waveform Generation Mode Combined with the WGM22 bit found in the TCCR2B Register, these bits control the counting sequence of the counter, the source for maximum (TOP) counter value, and what type of wave- ...

Page 159

... OCR2B as TOP. The FOC2B bit is always read as zero. • Bits 5:4 – Reserved These bits are reserved bits in the ATmega48P/88P/168P and will always read as zero. • Bit 3 – WGM22: Waveform Generation Mode See the description in the • Bit 2:0 – CS22:0: Clock Select ...

Page 160

... TCNT2[7:0] R/W R/W R/W R OCR2A[7:0] R/W R/W R/W R OCR2B[7:0] R/W R/W R/W R ATmega48P/88P/168P /(No prescaling) /8 (From prescaler) /32 (From prescaler) /64 (From prescaler) /128 (From prescaler) /256 (From prescaler) /1024 (From prescaler R/W R/W R/W R R/W R/W R/W R R/W R/W R/W R TCNT2 ...

Page 161

... Enable), and TOV2 are set (one), the Timer/Counter2 Overflow interrupt is executed. In PWM mode, this bit is set when Timer/Counter2 changes counting direction at 0x00. 8025L–AVR–7/ – – – – – – – – ATmega48P/88P/168P – OCIE2B OCIE2A TOIE2 R R/W R/W R – OCF2B OCF2A TOV2 R R/W R/W R TIMSK2 TIFR2 ...

Page 162

... If a write is performed to any of the five Timer/Counter2 Registers while its update busy flag is set, the updated value might get corrupted and cause an unintentional interrupt to occur. 8025L–AVR–7/ – EXCLK AS2 TCN2UB OCR2AUB R R/W R ATmega48P/88P/168P OCR2BUB TCR2AUB TCR2BUB When AS2 is I/O 0 ASSR R 0 162 ...

Page 163

... TSM bit is set. Refer to the description of the chronization Mode” on page 141 8025L–AVR–7/ TSM – – – R for a description of the Timer/Counter Synchronization mode. ATmega48P/88P/168P – – PSRASY PSRSYNC R R R/W R ”Bit 7 – TSM: Timer/Counter Syn- GTCCR 163 ...

Page 164

... Overview The Serial Peripheral Interface (SPI) allows high-speed synchronous data transfer between the ATmega48P/88P/168P and peripheral devices or between several AVR devices. The USART can also be used in Master SPI mode, see “USART in SPI Mode” on page 202. The PRSPI bit in module. ...

Page 165

... In SPI Slave mode, the control logic will sample the incoming signal of the SCK pin. To ensure correct sampling of the clock signal, the minimum low and high periods should be: Low periods: Longer than 2 CPU clock cycles. High periods: Longer than 2 CPU clock cycles. 8025L–AVR–7/10 ATmega48P/88P/168P Figure 18-2 on page SHIFT ENABLE 165 ...

Page 166

... SPI Pin Overrides Direction, Master SPI User Defined Input User Defined User Defined See ”Alternate Functions of Port B” on page 80 direction of the user defined SPI pins. ATmega48P/88P/168P Direction, Slave SPI Input User Defined Input Input for a detailed description of how to define the 166 ...

Page 167

... Set MOSI and SCK output, all others input */ DDR_SPI = (1<<DD_MOSI)|(1<<DD_SCK); /* Enable SPI, Master, set clock rate fck/16 */ SPCR = (1<<SPE)|(1<<MSTR)|(1<<SPR0); /* Start transmission */ SPDR = cData; /* Wait for transmission complete */ while(!(SPSR & (1<<SPIF))) ; 1. See ”About Code Examples” on page 8. ATmega48P/88P/168P 167 ...

Page 168

... Read received data and return in r16,SPDR ret (1) /* Set MISO output, all others input */ DDR_SPI = (1<<DD_MISO); /* Enable SPI */ SPCR = (1<<SPE); /* Wait for reception complete */ while(!(SPSR & (1<<SPIF))) ; /* Return Data Register */ return SPDR; 1. See ”About Code Examples” on page 8. ATmega48P/88P/168P 168 ...

Page 169

... Table 18-3 on page 171 and Table 18-4 on page SPI Modes Conditions 0 CPOL=0, CPHA=0 1 CPOL=0, CPHA=1 2 CPOL=1, CPHA=0 3 CPOL=1, CPHA=1 ATmega48P/88P/168P 171, as done in Table 18-2. Leading Edge Trailing eDge Sample (Rising) Setup (Falling) Setup (Rising) Sample (Falling) Sample (Falling) Setup (Rising) Setup (Falling) ...

Page 170

... SCK (CPOL = 0) mode 1 SCK (CPOL = 1) mode 3 SAMPLE I MOSI/MISO CHANGE 0 MOSI PIN CHANGE 0 MISO PIN SS MSB first (DORD = 0) MSB Bit 6 LSB first (DORD = 1) LSB Bit 1 ATmega48P/88P/168P Bit 4 Bit 3 Bit 2 Bit 1 LSB Bit 3 Bit 4 Bit 5 Bit 6 MSB Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 2 ...

Page 171

... Figure 18-3 and Figure 18-4 CPOL Functionality CPOL Leading Edge 0 Rising 1 Falling Figure 18-3 CPHA Functionality CPHA Leading Edge 0 Sample 1 Setup ATmega48P/88P/168P CPOL CPHA SPR1 SPR0 R/W R/W R/W R for an example. The CPOL functionality is sum- Trailing Edge Falling Rising and Figure 18-4 for an example ...

Page 172

... SPI Data Register. • Bit 5:1 – Reserved These bits are reserved bits in the ATmega48P/88P/168P and will always read as zero. • Bit 0 – SPI2X: Double SPI Speed Bit When this bit is written logic one the SPI speed (SCK Frequency) will be doubled when the SPI is in Master mode (see clock periods ...

Page 173

... The SPI Data Register is a read/write register used for data transfer between the Register File and the SPI Shift Register. Writing to the register initiates data transmission. Reading the regis- ter causes the Shift Register Receive buffer to be read. 8025L–AVR–7/ MSB R/W R/W R/W R ATmega48P/88P/168P LSB R/W R/W R/W R SPDR Undefined 173 ...

Page 174

... Receiver includes a Parity Checker, Control logic, a Shift Register and a two level receive buffer (UDRn). The Receiver supports the same frame formats as the Transmitter, and can detect Frame Error, Data OverRun and Parity Errors. 8025L–AVR–7/10 ATmega48P/88P/168P ”Minimizing Power Consumption” on page 43 Figure 19-1 on page 175. CPU ...

Page 175

... The XCKn pin is only active when using synchronous mode. 8025L–AVR–7/10 (1) UBRRn [H:L] BAUD RATE GENERATOR UDRn(Transmit) TRANSMIT SHIFT REGISTER RECEIVE SHIFT REGISTER UDRn (Receive) UCSRnA 1. Refer to Figure 1-1 on page 2 and ATmega48P/88P/168P Clock Generator OSC SYNC LOGIC PIN CONTROL Transmitter TX CONTROL PARITY GENERATOR PIN CONTROL ...

Page 176

... Pin DDR_XCKn UCPOLn Transmitter clock (Internal Signal). Receiver base clock (Internal Signal). Input from XCK pin (internal Signal). Used for synchronous slave Clock output to XCK pin (Internal Signal). Used for synchronous master operation. XTAL pin frequency (System Clock). ATmega48P/88P/168P U2Xn / DDR_XCKn 0 ...

Page 177

... BAUD BAUD BAUD 1. The baud rate is defined to be the transfer rate in bit per second (bps) Baud rate (in bits per second, bps) System Oscillator clock frequency Contents of the UBRRnH and UBRRnL Registers, (0-4095) 198). ATmega48P/88P/168P Equation for Calculating (1) Rate UBRRn Value UBRRn = f ...

Page 178

... Figure 19-2 for details. depends on the stability of the system clock source therefore recommended to osc UCPOL = 1 XCK RxD / TxD UCPOL = 0 XCK RxD / TxD Figure 19-3 shows, when UCPOLn is zero the data will be changed at ATmega48P/88P/168P f OSC < ---------- - f XCK 4 Sample Sample 178 ...

Page 179

... No transfers on the communication line (RxDn or TxDn). An IDLE line high. ⊕ even n 1 – ⊕ odd – Parity bit using even parity even odd Parity bit using odd parity Data bit n of the character n ATmega48P/88P/168P FRAME 4 [5] [6] [7] [8] [P] Sp1 [Sp2] … ⊕ ⊕ ⊕ ⊕ ⊕ ...

Page 180

... The following simple USART initialization code examples show one assembly and one C func- tion that are equal in functionality. The examples assume asynchronous operation using polling (no interrupts enabled) and a fixed frame format. The baud rate is given as a function parameter. 8025L–AVR–7/10 ATmega48P/88P/168P 180 ...

Page 181

... USART_Init(MYUBRR) /*Set baud rate */ UBRR0H = (unsigned char)(ubrr>>8); UBRR0L = (unsigned char)ubrr; Enable receiver and transmitter */ UCSR0B = (1<<RXEN0)|(1<<TXEN0); /* Set frame format: 8data, 2stop bit */ UCSR0C = (1<<USBS0)|(3<<UCSZ00); 1. See ”About Code Examples” on page 8. ATmega48P/88P/168P 181 ...

Page 182

... UCSRnA,UDREn rjmp USART_Transmit ; Put data (r16) into buffer, sends the data out UDRn,r16 ret (1) /* Wait for empty transmit buffer */ while ( !( UCSRnA & (1<<UDREn Put data into buffer, sends the data */ UDRn = data; 1. See ”About Code Examples” on page 8. ATmega48P/88P/168P 182 ...

Page 183

... Put data into buffer, sends the data */ UDRn = data; 1. These transmit functions are written to be general functions. They can be optimized if the con- tents of the UCSRnB is static. For example, only the TXB8 bit of the UCSRnB Register is used after initialization. 2. See ”About Code Examples” on page 8. ATmega48P/88P/168P 183 ...

Page 184

... UDRn I/O location. The following code example shows a simple USART receive function based on polling of the Receive Complete (RXCn) Flag. When using frames with less than eight bits the most significant 8025L–AVR–7/10 ATmega48P/88P/168P 184 ...

Page 185

... For I/O Registers located in extended I/O map, “IN”, “OUT”, “SBIS”, “SBIC”, “CBI”, and “SBI” instructions must be replaced with instructions that allow access to extended I/O. Typically “LDS” and “STS” combined with “SBRS”, “SBRC”, “SBR”, and “CBR”. ATmega48P/88P/168P 185 ...

Page 186

... For I/O Registers located in extended I/O map, “IN”, “OUT”, “SBIS”, “SBIC”, “CBI”, and “SBI” instructions must be replaced with instructions that allow access to extended I/O. Typically “LDS” and “STS” combined with “SBRS”, “SBRC”, “SBR”, and “CBR”. ATmega48P/88P/168P 186 ...

Page 187

... The result of the check is stored in the receive buffer together with the received data and stop bits. The Parity Error (UPEn) Flag can then be read by software to check if the frame had a Parity Error. 8025L–AVR–7/10 ”Parity Bit Calculation” on page 179 ATmega48P/88P/168P and ”Parity Checker” on page 187. 187 ...

Page 188

... For I/O Registers located in extended I/O map, “IN”, “OUT”, “SBIS”, “SBIC”, “CBI”, and “SBI” instructions must be replaced with instructions that allow access to extended I/O. Typically “LDS” and “STS” combined with “SBRS”, “SBRC”, “SBR”, and “CBR”. ATmega48P/88P/168P Figure 19-5 188 ...

Page 189

... RxD IDLE Sample (U2X = Sample (U2X = RxD Sample (U2X = Sample (U2X = shows the sampling of the stop bit and the earliest possible beginning ATmega48P/88P/168P START Figure 19-6 shows the sampling of the data bits and BIT ...

Page 190

... Double Speed mode the ratio of the slowest incoming data rate that can be accepted in relation to the receiver baud rate the ratio of the fastest incoming data rate that can be fast accepted in relation to the receiver baud rate. and Table 19-3 on page 191 ATmega48P/88P/168P STOP 1 (A) ( ...

Page 191

... ATmega48P/88P/168P Recommended Max Max Total Error (%) Receiver Error (%) +6.67/-6.8 ± 3.0 +5.79/-5.88 ± 2.5 +5.11/-5.19 ± 2.0 +4.58/-4.54 ± 2.0 +4.14/-4.19 ± 1.5 +3.78/-3.83 ± 1.5 ...

Page 192

... Do not use Read-Modify-Write instructions (SBI and CBI) to set or clear the MPCMn bit. The MPCMn bit shares the same I/O location as the TXCn Flag and this might accidentally be cleared when using SBI or CBI instructions. 8025L–AVR–7/10 ATmega48P/88P/168P 192 ...

Page 193

... The UDREn Flag can generate a 8025L–AVR–7/ RXB[7:0] TXB[7:0] R/W R/W R/W R RXCn TXCn UDREn FEn R R ATmega48P/88P/168P R/W R/W R/W R DORn UPEn U2Xn MPCMn R R R/W R UDRn (Read) UDRn (Write) UCSRnA ...

Page 194

... TXCIEn bit is written to one, the Global Interrupt Flag in SREG is written to one and the TXCn bit in UCSRnA is set. 8025L–AVR–7/10 ”Multi-processor Communication Mode” on page RXCIEn TXCIEn UDRIEn RXENn R/W R/W R/W R ATmega48P/88P/168P 191 TXENn UCSZn2 RXB8n TXB8n R/W R UCSRnB 194 ...

Page 195

... UMSELn1 UMSELn0 UPMn1 R/W R/W R UMSELn Bits Settings UMSELn0 See ”USART in SPI Mode” on page 202 operation ATmega48P/88P/168P UPMn0 USBSn UCSZn1 UCSZn0 R/W R/W R/W R Table 19-4. Mode Asynchronous USART Synchronous USART (Reserved) (1) Master SPI (MSPIM) for full description of the Master SPI Mode (MSPIM) ...

Page 196

... UPMn Bits Settings UPMn1 UPMn0 USBS Bit Settings USBSn 0 1 UCSZn Bits Settings UCSZn1 ATmega48P/88P/168P Parity Mode Disabled Reserved Enabled, Even Parity Enabled, Odd Parity Stop Bit(s) 1-bit 2-bit UCSZn0 Character Size 0 5-bit 1 6-bit 0 7-bit 1 8-bit 0 Reserved 1 Reserved 0 Reserved 1 9-bit 196 ...

Page 197

... R/W R/W R/W R 190). The error values are calculated using the following equation: BaudRate ⎛ Closest Match Error[%] = ------------------------------------------------- - 1 ⎝ BaudRate ATmega48P/88P/168P Received Data Sampled (Input on RxDn Pin) Falling XCKn Edge Rising XCKn Edge UBRRn[11: R/W R/W R/W R/W R/W R/W R/W ...

Page 198

... ATmega48P/88P/168P f = 2.0000 MHz osc U2Xn = 1 U2Xn = 0 UBRRn Error UBRRn Error 95 0.0% 51 0.2% 47 0.0% 25 0.2% 23 0.0% 12 0.2% 15 0.0% 8 -3.5% 11 ...

Page 199

... Mbps ATmega48P/88P/168P f = 7.3728 MHz osc U2Xn = 0 U2Xn = 1 Error UBRRn Error UBRRn 0.2% 191 0.0% 383 0.2% 95 0.0% 191 0.2% 47 0.0% 95 -0.8% 31 0. ...

Page 200

... Mbps ATmega48P/88P/168P f = 14.7456 MHz osc U2Xn = 0 U2Xn = 1 Error UBRRn Error UBRRn 0.0% 383 0.0% 767 0.0% 191 0.0% 383 0.0% 95 0.0% 191 0.0% 63 0.0% 127 0 ...