ATF22V10C-10XU Atmel, ATF22V10C-10XU Datasheet - Page 9

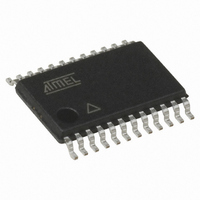

ATF22V10C-10XU

Manufacturer Part Number

ATF22V10C-10XU

Description

IC PLD 10NS 24TSSOP

Manufacturer

Atmel

Datasheet

1.ATF22V10C-10JU.pdf

(22 pages)

Specifications of ATF22V10C-10XU

Programmable Type

EE PLD

Number Of Macrocells

10

Voltage - Input

5V

Speed

10ns

Mounting Type

Surface Mount

Package / Case

24-TSSOP

Logic Family

ATF22V10C

Maximum Operating Frequency

125 MHz

Number Of Programmable I/os

10

Delay Time

10 ns

Operating Supply Voltage

5 V

Maximum Operating Temperature

+ 85 C

Minimum Operating Temperature

- 40 C

Mounting Style

SMD/SMT

Number Of Product Terms Per Macro

16

Supply Voltage (max)

5.5 V

Supply Voltage (min)

4.5 V

Family Name

ATF22V10C

Process Technology

EECMOS

# Macrocells

10

# I/os (max)

10

Frequency (max)

125MHz

Propagation Delay Time

10ns

Operating Supply Voltage (typ)

5V

Operating Supply Voltage (min)

4.5V

Operating Supply Voltage (max)

5.5V

Operating Temp Range

-40C to 85C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

24

Package Type

TSSOP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ATF22V10C-10XU

Manufacturer:

ATMEL

Quantity:

100

0735U–PLD–7/10

9.

10.

Power-down Mode

The Atmel

PD pin acts as the power-down pin (Pin 4 on the DIP/SOIC packages and Pin 5 on the PLCC package). When the

PD pin is high, the device supply current is reduced to less than 100mA. During power-down, all output data and

internal logic states are latched and held. Therefore, all registered and combinatorial output data remain valid. Any

outputs that were in an undetermined state at the onset of power-down will remain at the same state. During

power-down, all input signals except the power-down pin are blocked. Input and I/O hold latches remain active to

ensure that pins do not float to indeterminate levels, further reducing system power. The power-down pin feature is

enabled in the logic design file. Designs using the power-down pin may not use the PD pin logic array input.

However, all other PD pin macrocell resources may still be used, including the buried feedback and foldback

product term array inputs.

PD pin configuration is controlled by the design file, and appears as a separate fuse bit in the JEDEC file. When

the power-down feature is not specified in the design file, the IN/PD pin will be configured as a regular logic input.

Note:

Compiler Mode Selection

Table 10-1.

Note:

Synario

WINCUPL

Some programmers list the 22V10 JEDEC compatible 22V10C (no PD used) separately from the non-22V10 JEDEC

compatible 22V10CEX (with PD used)

1. These device types will create a JEDEC file which when programmed in Atmel ATF22V10C devices will enable the

®

power-down mode feature. All other device types have the feature disabled

ATF22V10C includes an optional pin-controlled power-down feature. When this mode is enabled, the

Compiler Mode Selection

ATF22V10C (DIP)

ATF22V10C (PLCC)

P22V10

P22V10LCC

(5828 Fuses)

PAL Mode

ATTF22V10C DIP (UES)

ATF22C10C PLCC (UES)

G22V10

G22V10LCC

(5892 Fuses)

GAL Mode

Atmel ATF22V10C(Q)

ATF22V10C DIP (PWD)

ATF22V10C PLCC (PWD)

G22V10CP

G22V10CPLCC

Power-down Mode

(5893 Fuses)

(1)

9