MAX145ACUA+ Maxim Integrated Products, MAX145ACUA+ Datasheet - Page 11

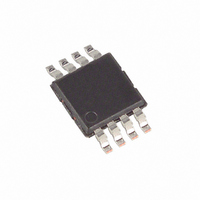

MAX145ACUA+

Manufacturer Part Number

MAX145ACUA+

Description

IC ADC 12BIT 108KSPS 8-UMAX

Manufacturer

Maxim Integrated Products

Datasheet

1.MAX144BEUA.pdf

(16 pages)

Specifications of MAX145ACUA+

Number Of Bits

12

Sampling Rate (per Second)

108k

Data Interface

MICROWIRE™, QSPI™, Serial, SPI™

Number Of Converters

1

Power Dissipation (max)

330mW

Voltage Supply Source

Single Supply

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

8-TSSOP, 8-MSOP (0.118", 3.00mm Width)

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

4) Pull CS/SHDN high at or after the 16th falling clock

5) With CS/SHDN high, wait at least 60ns (t

Data can be output in two 8-bit sequences or continu-

ously. The bytes will contain the result of the conversion

Figure 7. Detailed Serial-Interface Timing Sequence

Figure 8a. SPI Connections

Figure 8c. SPI/MICROWIRE Interface Timing Sequence (CPOL = CPHA = 0)

CS/SHDN

CS/SHDN

*WHEN CS/SHDN IS HIGH, DOUT = HIGH-Z

DOUT valid timing characteristic. Data should be

clocked into the µP on SCLK’s rising edge.

edge. If CS/SHDN remains low, trailing zeros will be

clocked out after the LSB.

starting a new conversion by pulling CS/SHDN low.

A conversion can be aborted by pulling CS/SHDN

high before the conversion ends; wait at least 60ns

before starting a new conversion.

DOUT*

DOUT

SCLK

SCLK

SPI

HIGH-Z

t

SCLKS

MISO

SCK

I/O

SS

______________________________________________________________________________________

+2.7V, Low-Power, 2-Channel, 108ksps,

t

1

DV

SAMPLING INSTANT

V

DD

2

3

CHID D11

1ST BYTE READ

Serial 12-Bit ADCs in 8-Pin µMAX

4

CS/SHDN

SCLK

DOUT

MSB

t

CL

MAX144

MAX145

5

D10

CS

6

) before

t

CH

D9

7

D8

8

padded with three leading ones and the channel identi-

fication before the MSB. If the serial clock hasn’t been

idled after the last LSB and CS/SHDN is kept low,

DOUT sends trailing zeros.

When using SPI (Figure 8a) or MICROWIRE (Figure 8b)

interfaces, set CPOL = 0 and CPHA = 0. Conversion

begins with a falling edge on CS/SHDN (Figure 8c).

Two consecutive 8-bit readings are necessary to obtain

the entire 12-bit result from the ADC. DOUT data transi-

tions on the serial clock’s falling edge and is clocked

into the µP on SCLK’s rising edge. The first 8-bit data

stream contains three leading ones, the channel identi-

8b. MICROWIRE Connections

D7

MICROWIRE

9

D6

t

DO

I/O

SK

10

SI

D5

11

SPI and MICROWIRE Interface

2ND BYTE READ

D4

12

D3

13

D2

14

CS/SHDN

SCLK

DOUT

t

D1

TR

15

MAX144

MAX145

t

CS

LSB

D0

16

HIGH-Z

HIGH-Z

11