XC2S100E-6FTG256C Xilinx Inc, XC2S100E-6FTG256C Datasheet - Page 108

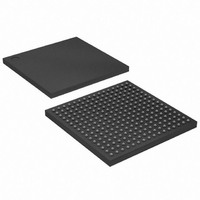

XC2S100E-6FTG256C

Manufacturer Part Number

XC2S100E-6FTG256C

Description

FPGA Spartan®-IIE Family 100K Gates 2700 Cells 357MHz 0.15um Technology 1.8V 256-Pin FTBGA

Manufacturer

Xilinx Inc

Series

Spartan™-IIEr

Datasheet

1.XC2S50E-6TQG144C.pdf

(108 pages)

Specifications of XC2S100E-6FTG256C

Package

256FTBGA

Family Name

Spartan®-IIE

Device Logic Cells

2700

Device Logic Units

600

Device System Gates

100000

Maximum Internal Frequency

357 MHz

Typical Operating Supply Voltage

1.8 V

Maximum Number Of User I/os

182

Ram Bits

40960

Number Of Logic Elements/cells

2700

Number Of Labs/clbs

600

Total Ram Bits

40960

Number Of I /o

182

Number Of Gates

100000

Voltage - Supply

1.71 V ~ 1.89 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

256-LBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

122-1322

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XC2S100E-6FTG256C

Manufacturer:

Xilinx Inc

Quantity:

10 000

Spartan-IIE FPGA Family: Pinout Tables

Revision History

108

Version

No.

1.0

1.1

2.0

2.1

2.3

11/15/01

12/20/01

11/18/02

02/14/03

06/18/08

Date

Initial Xilinx release.

Corrected differential pin pair designations.

Added XC2S400E and XC2S600E and FG676. Removed L37 designation from FT256 pinouts.

Minor corrections and clarifications to pinout definitions. Removed Preliminary designation.

Added differential pairs table on

Clarified that XC2S50E has two VREF pins per bank.

Added

numbering. Updated links. Synchronized all modules to v2.3.

Package Overview

section. Updated all modules for continuous page, figure, and table

www.xilinx.com

page

57, fixed 3 P/N designation typos introduced in v2.0.

Description

DS077-4 (2.3) June 18, 2008

Product Specification

R