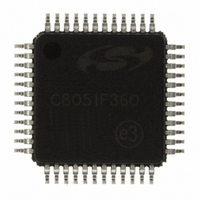

C8051F360-GQ Silicon Laboratories Inc, C8051F360-GQ Datasheet - Page 234

C8051F360-GQ

Manufacturer Part Number

C8051F360-GQ

Description

IC 8051 MCU 32K FLASH 48TQFP

Manufacturer

Silicon Laboratories Inc

Series

C8051F36xr

Specifications of C8051F360-GQ

Program Memory Type

FLASH

Program Memory Size

32KB (32K x 8)

Package / Case

48-TQFP, 48-VQFP

Core Processor

8051

Core Size

8-Bit

Speed

100MHz

Connectivity

EBI/EMI, SMBus (2-Wire/I²C), SPI, UART/USART

Peripherals

POR, PWM, Temp Sensor, WDT

Number Of I /o

39

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 3.6 V

Data Converters

A/D 17x10b; D/A 1x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Processor Series

C8051F3x

Core

8051

Data Bus Width

8 bit

Data Ram Size

1 KB

Interface Type

I2C/SMBus/SPI/UART

Maximum Clock Frequency

100 MHz

Number Of Programmable I/os

39

Number Of Timers

4

Operating Supply Voltage

3 V to 3.6 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

KSK-SL-TOOLSTICK, PK51, CA51, A51, ULINK2

Development Tools By Supplier

C8051F360DK

Minimum Operating Temperature

- 40 C

On-chip Adc

21-ch x 10-bit

On-chip Dac

1-ch x 10-bit

Package

48TQFP

Device Core

8051

Family Name

C8051F36x

Maximum Speed

100 MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

336-1483 - ADAPTER PROGRAM TOOLSTICK F360770-1006 - ISP 4PORT FOR SILABS C8051F MCU336-1412 - BOARD TARGET/PROTO W/C8051F360336-1411 - DAUGHTER CARD TOOLSTCK C8051F362336-1410 - KIT DEV FOR C8051F360 FAMILY

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

336-1407

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

C8051F360-GQ

Manufacturer:

Silicon Laboratories Inc

Quantity:

10 000

Part Number:

C8051F360-GQ

Manufacturer:

SILICON LABS/芯科

Quantity:

20 000

Company:

Part Number:

C8051F360-GQR

Manufacturer:

Silicon Laboratories Inc

Quantity:

10 000

Part Number:

C8051F360-GQR

Manufacturer:

SILICON LABS/芯科

Quantity:

20 000

- Current page: 234 of 288

- Download datasheet (3Mb)

C8051F360/1/2/3/4/5/6/7/8/9

20. Enhanced Serial Peripheral Interface (SPI0)

The Enhanced Serial Peripheral Interface (SPI0) provides access to a flexible, full-duplex synchronous

serial bus. SPI0 can operate as a master or slave device in both 3-wire or 4-wire modes, and supports mul-

tiple masters and slaves on a single SPI bus. The slave-select (NSS) signal can be configured as an input

to select SPI0 in slave mode, or to disable Master Mode operation in a multi-master environment, avoiding

contention on the SPI bus when more than one master attempts simultaneous data transfers. NSS can

also be configured as a chip-select output in master mode, or disabled for 3-wire operation. Additional gen-

eral purpose port I/O pins can be used to select multiple slave devices in master mode.

234

SYSCLK

Clock Divide

SPI0CKR

SFR Bus

SPI0DAT

Logic

Write

Transmit Data Buffer

Receive Data Buffer

Figure 20.1. SPI Block Diagram

7

6

Shift Register

5

SPI CONTROL LOGIC

4

3

Data Path

2

SFR Bus

SPI0CFG

Control

SPI0DAT

1

SPI0DAT

Read

0

Rev. 1.0

Tx Data

Rx Data

Pin Interface

Control

Control

Logic

Pin

SPI0CN

MOSI

MISO

SCK

NSS

O

C

R

S

S

B

A

R

SPI IRQ

Port I/O

Related parts for C8051F360-GQ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

SMD/C°/SINGLE-ENDED OUTPUT SILICON OSCILLATOR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 AES KEYFOB DEMO WITH LCD RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 SIMPLIFIED KEY FOB DEMO WITH LED RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A/-40 TO 85 OC/EZLINK MODULE; F930/4432 HIGH BAND (REV E/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

EZLink Module; F930/4432 Low Band (rev e/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4460 10 DBM RADIO TEST CARD 434 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4461 14 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RFSWITCH RADIO TEST CARD 460 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 27 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 SKYWORKS 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

N/A N/A/-40 TO 85 OC/4463 RFMD 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 169 MHZ

Manufacturer:

Silicon Laboratories Inc