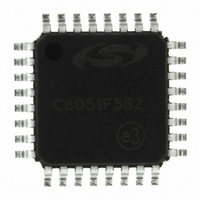

C8051F562-IQ Silicon Laboratories Inc, C8051F562-IQ Datasheet - Page 83

C8051F562-IQ

Manufacturer Part Number

C8051F562-IQ

Description

IC 8051 MCU 32K FLASH 32-QFP

Manufacturer

Silicon Laboratories Inc

Series

C8051F56xr

Specifications of C8051F562-IQ

Program Memory Type

FLASH

Program Memory Size

32KB (32K x 8)

Package / Case

32-QFP

Core Processor

8051

Core Size

8-Bit

Speed

50MHz

Connectivity

SMBus (2-Wire/I²C), LIN, SPI, UART/USART

Peripherals

POR, PWM, Temp Sensor, WDT

Number Of I /o

25

Ram Size

2.25K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.25 V

Data Converters

A/D 25x12b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 125°C

Processor Series

C8051F5x

Core

8051

Data Bus Width

8 bit

Data Ram Size

2304 B

Maximum Clock Frequency

50 MHz

Number Of Programmable I/os

25

Operating Supply Voltage

1.8 V to 5.25 V

Maximum Operating Temperature

+ 125 C

Mounting Style

SMD/SMT

3rd Party Development Tools

PK51, CA51, A51, ULINK2

Development Tools By Supplier

C8051F560DK

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

336-1691 - KIT DEVELOPMENT FOR C8051F560

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

336-1698

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

C8051F562-IQ

Manufacturer:

Silicon Laboratories Inc

Quantity:

10 000

Company:

Part Number:

C8051F562-IQR

Manufacturer:

Silicon Laboratories Inc

Quantity:

10 000

- Current page: 83 of 302

- Download datasheet (3Mb)

C8051F55x/56x/57x

10.2. Instruction Set

The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51™ instruc-

tion set. Standard 8051 development tools can be used to develop software for the CIP-51. All CIP-51

instructions are the binary and functional equivalent of their MCS-51™ counterparts, including opcodes,

addressing modes and effect on PSW flags. However, instruction timing is different than that of the stan-

dard 8051.

10.2.1. Instruction and CPU Timing

In many 8051 implementations, a distinction is made between machine cycles and clock cycles, with

machine cycles varying from 2 to 12 clock cycles in length. However, the CIP-51 implementation is based

solely on clock cycle timing. All instruction timings are specified in terms of clock cycles.

Due to the pipelined architecture of the CIP-51, most instructions execute in the same number of clock

cycles as there are program bytes in the instruction. Conditional branch instructions take one less clock

cycle to complete when the branch is not taken as opposed to when the branch is taken. Table 10.1 is the

CIP-51 Instruction Set Summary, which includes the mnemonic, number of bytes, and number of clock

cycles for each instruction.

Rev. 1.1

83

Related parts for C8051F562-IQ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

SMD/C°/SINGLE-ENDED OUTPUT SILICON OSCILLATOR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 AES KEYFOB DEMO WITH LCD RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 SIMPLIFIED KEY FOB DEMO WITH LED RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A/-40 TO 85 OC/EZLINK MODULE; F930/4432 HIGH BAND (REV E/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

EZLink Module; F930/4432 Low Band (rev e/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4460 10 DBM RADIO TEST CARD 434 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4461 14 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RFSWITCH RADIO TEST CARD 460 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 27 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 SKYWORKS 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

N/A N/A/-40 TO 85 OC/4463 RFMD 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 169 MHZ

Manufacturer:

Silicon Laboratories Inc