LH28F640SPHT-PTL12 Sharp Microelectronics, LH28F640SPHT-PTL12 Datasheet - Page 26

LH28F640SPHT-PTL12

Manufacturer Part Number

LH28F640SPHT-PTL12

Description

IC FLASH 64MBIT 120NS 56TSOP

Manufacturer

Sharp Microelectronics

Datasheet

1.LH28F640SPHT-PTL12.pdf

(45 pages)

Specifications of LH28F640SPHT-PTL12

Rohs Status

RoHS non-compliant

Format - Memory

FLASH

Memory Type

Page Mode FLASH

Memory Size

64M (8Mx8, 4Mx16)

Speed

120ns

Interface

Parallel

Operating Temperature

-40°C ~ 85°C

Package / Case

56-TSOP

Voltage - Supply

-

Other names

425-1857

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LH28F640SPHT-PTL12

Manufacturer:

SHARP

Quantity:

998

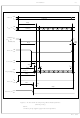

1.2.5 AC Characteristics - Write Operations

NOTES:

1. The timing characteristics for reading the status register during block erase, (page buffer) program, block lock

2. A write operation can be initiated and terminated with either CE

3. Sampled, not 100% tested.

4. Write pulse width low (t

5. Write pulse width high (t

6. V

7. Refer to Table 5 for valid address and data for block erase, (page buffer) program, block lock configuration and OTP

8. The output delay time t

9. The timing is defined from the first edge of CE

10. The timing is defined from the first edge of CE

11. STS timings depend on STS configuration.

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

(t

t

(t

AVAV

PHWL

ELWL

WLWH

DVWH

AVWH

WHEH

WHDX

WHAX

WHWL

VVWH

WHGL

WHR0

WHRL

QVVL

FLWH

WHFL

FLEH

EHFL

configuration and OTP program operations are the same as during read-only operations. Refer to AC Characteristics for

read-only operations.

of WE# (whichever occurs last) to the first edge of CE

(whichever occurs first). Hence, t

of WE# (whichever occurs first) to the first edge of CE

(whichever occurs last). Hence, t

or OTP program success (SR.1/3/4/5=0).

program.

PEN

Symbol

/t

/t

/t

/t

(t

(t

(t

(t

(t

(t

(t

(t

(t

(t

(t

(t

FHWH

(t

WHFH

should be held at V

FHEH

EHFH

WLEL

PHEL

EHR0

EHRL

AVEH

EHWH

EHGL

ELEH

DVEH

EHDX

EHAX

VVEH

EHEL

)

)

)

)

)

)

)

)

)

)

)

)

)

)

)

Write Cycle Time

RP# High Recovery to WE# (CE

CE

WE# (CE

Data Setup to WE# (CE

Address Setup to WE# (CE

CE

Data Hold from WE# (CE

Address Hold from WE# (CE

WE# (CE

V

Write Recovery before Read

WE# (CE

V

BYTE# Setup to WE# (CE

BYTE# Hold from WE# (CE

PEN

PEN

X

X

AVQV

WP

WPH

(WE#) Setup to WE# (CE

(WE#) Hold from WE# (CE

PEN

Setup to WE# (CE

Hold from Valid SRD, STS High Z

) is defined from the first edge of CE

) is defined from the first edge of CE

X

X

X

=V

or t

) Pulse Width Low

) Pulse Width High

) High to SR.7 Going "0", STS Going Low

PENH

ELQV

WPH

WP

=t

=t

WLWH

until determination of block erase, (page buffer) program, block lock configuration

is required in addition to t

WHWL

V

CC

Parameter

X

X

=t

) Going High

=2.7V-3.6V, T

=t

X

) Going High

X

ELEH

0

X

) High

EHEL

, CE

) Going High

0

) Going High

X

, CE

X

) High

) High

X

=t

X

(1), (2)

) Going Low

1

LHF64P01

=t

X

) Going Low

1

WLEH

or CE

) High

WHEL

or CE

0

0

, CE

, CE

A

=t

2

=-40 C to +85 C

=t

1

1

2

that enables the device.

ELWH

or CE

that disables the device.

or CE

EHWL

0

WHGL

0

, CE

, CE

0

, CE

.

.

2

2

1

1

, CE

that disables the device or the rising edge of WE#

that enables the device or the falling edge of WE#

(t

1

or CE

EHGL

or CE

2

or WE#.

2

) for read operations after command writes.

2

that enables the device or the falling edge

that disables the device or the rising edge

4, 9, 10

5, 9, 10

3, 6, 11

10, 11

Notes

7, 10

7, 10

3, 10

3, 9

10

10

10

10

10

9

8

Min.

120

70

50

55

30

35

50

90

1

0

0

0

0

0

0

Max.

500

Rev. 0.06

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

s

24