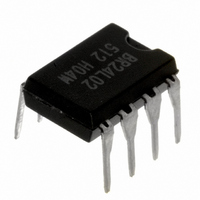

BR24L02-W Rohm Semiconductor, BR24L02-W Datasheet - Page 29

BR24L02-W

Manufacturer Part Number

BR24L02-W

Description

IC EEPROM 2KBIT 400KHZ 8DIP

Manufacturer

Rohm Semiconductor

Datasheet

1.BR24L08F-WE2.pdf

(33 pages)

Specifications of BR24L02-W

Format - Memory

EEPROMs - Serial

Memory Type

EEPROM

Memory Size

2K (256 x 8)

Speed

400kHz

Interface

I²C, 2-Wire Serial

Voltage - Supply

1.8 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Package / Case

8-DIP (0.300", 7.62mm)

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

BR24L02-W

Manufacturer:

ROHM/罗姆

Quantity:

20 000

● Cautions on microcontroller connection

○ Rs

○ Maximum value of Rs

○ Maximum value of Rs

The maximum value of Rs is determined by following relations.

The minimum value of Rs is determined by over current at bus collision. When over current flows, noises in power source line,

and instantaneous power failure of power source may occur. When allowable over current is defined as I, the following relation

must be satisfied. Determine the allowable current in consideration of impedance of power source line in set and so forth. Set

the over current to EEPROM 10mA or below.

In I

state to SDA port, insert a series resistance Rs between the pull up resistance Rpu and the SDA terminal of EEPROM. This is

controls over current that occurs when PMOS of the microcontroller and NMOS of EEPROM are turned ON simultaneously. Rs

also plays the role of protection of SDA terminal against surge. Therefore, even when SDA port is open drain input/output, Rs

can be used.

(1)SDA rise time to be determined by the capacity (CBUS) of bus line of Rpu and SDA shoulder be tR or below.

(2)The bus electric potential A to be determined by Rpu and Rs the moment when EEPROM outputs 'L' to SDA bus should

2

C BUS, it is recommended that SDA port is of open drain input/output. However, when to use CMOS input / output of tri

And AC timing should be satisfied even when SDA rise time is late.

sufficiently secure the input 'L' level (V

V

IL

Microcontroller

Microcontroller

Fig.50 I/O circuit diagram

'H' output

Microcontroller

Fig.52 I/O circuit diagram

V

R

CC

PU

Fig.53 I/O circuit diagram

Bus line

capacity CBUS

R

R

Over current Ⅰ

PU

S

R

I

OL

S

R

EEPROM

A

PU

R

S

IL

EEPROM

) of microcontroller including recommended noise margin 0.1Vcc.

EEPROM

'L' output

V

OL

29/32

Example)

from(2),

SCL

SDA

'H' output of microcontroller

When V

(V

∴

∴

CC

R

R

R

-V

Example)When V

V

R

R

PU

S

S

CC

S

S

CC

+R

OL

≦

≦

≦

=3V, V

≦

≧

)×R

S

Fig.51 Input/output collision timing

1.67[kΩ]

0.3×3-0.4-0.1×3

V

Over current flows to SDA line by 'H'

output of microcontroller and 'L' output

of EEPROM.

S

V

R

IL

CC

1.1×3-0.3×3

I

I

-V

S

1.1V

IL

+ V

=0.3V

OL

≧

≧ 300[Ω]

CC

-0.1V

CC

OL

-V

'L' output of EEPROM

10×10

ACK

CC,

=3V, I=10mA

+0.1V

IL

3

V

CC

-3

OL

CC

=0.4V, R

≦V

×

×

IL

R

20×10

PU

PU

=20kΩ,

3