LPC-P2919 Olimex Ltd., LPC-P2919 Datasheet - Page 16

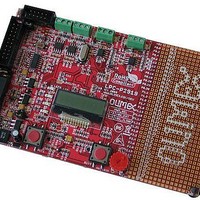

LPC-P2919

Manufacturer Part Number

LPC-P2919

Description

MCU, MPU & DSP Development Tools DEV BRD FOR LPC2919 768KB FLASH 56KBSRAM

Manufacturer

Olimex Ltd.

Datasheet

1.LPC-P2919.pdf

(21 pages)

Specifications of LPC-P2919

Processor To Be Evaluated

LPC2919 ARM968E-S

Data Bus Width

16 bit, 32 bit

Interface Type

RS-232, CAN, SPI

Dimensions

140 mm x 89 mm

Operating Supply Voltage

9 V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

I2C

SPI

serial clock line (SCL) and a serial data line (SDA). Each device is recognized by a

unique address and can operate as either a receiver-only device or as a transmitter

with the capability to both receive and send information (such as memory).

Transmitters and/or receivers can operate in either master or slave mode,

depending on whether the chip has to initiate a data transfer or is only addressed.

The I

connected to it.

–

–

–

–

–

–

–

–

–

allow synchronous serial communication with slave or master peripherals.

–

–

–

–

–

–

–

–

I

bus) and do not support powering off of individual devices connected to the

same bus lines.

Easy to configure as master, slave, or master/slave.

Programmable clocks allow versatile rate control.

Bidirectional data transfer between masters and slaves.

Multi-master bus (no central master).

Arbitration between simultaneously transmitting masters without corruption of

serial data on the bus.

Serial clock synchronization allows devices with different bit rates to

communicate via one serial bus.

Serial clock synchronization can be used as a handshake mechanism to suspend

and resume serial transfer.

All I

mode.

Master or slave operation.

Each SPI supports up to four slaves in sequential multi-slave operation.

Supports timer-triggered operation.

Programmable clock bit rate and prescale based on SPI source clock

(BASE_SPI_CLK), independent of system clock.

Separate transmit and receive FIFO memory buffers; 16 bits wide, 32 locations

deep.

Programmable choice of interface operation: Motorola SPI or Texas Instruments

Synchronous Serial Interfaces.

Programmable data-frame size from 4 to 16 bits.

Independent masking of transmit FIFO, receive FIFO and receive overrun

interrupts.

2

2

C0 and I

C is a multi-master bus, and it can be controlled by more than one bus master

The LPC2919 contain two I

The I

The main features if the I

The LPC2919 contains three Serial Peripheral Interface modules (SPIs) to

The key features are:

2

C-bus controllers support multiple address recognition and a bus monitor

2

C-bus is bidirectional for inter-IC control using only two wires: a

2

C1 use standard I/O pins with bit rates of up to 400 kbit/s (Fast I

Page 16

2

C-bus interfaces are:

2

C-bus controllers.

2

C-