TMP86FS28DFG(JZ) Toshiba, TMP86FS28DFG(JZ) Datasheet - Page 92

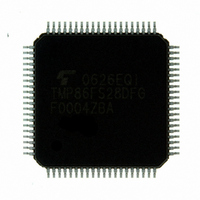

TMP86FS28DFG(JZ)

Manufacturer Part Number

TMP86FS28DFG(JZ)

Description

IC MCU 8BIT FLASH 60KB 80-LQFP

Manufacturer

Toshiba

Series

TLCS-870/Cr

Datasheet

1.TMP86FS28DFGJZ.pdf

(272 pages)

Specifications of TMP86FS28DFG(JZ)

Core Processor

870/C

Core Size

8-Bit

Speed

16MHz

Connectivity

SIO, UART/USART

Peripherals

LCD, PWM, WDT

Number Of I /o

62

Program Memory Size

60KB (60K x 8)

Program Memory Type

FLASH

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-LQFP

Processor Series

TLCS-870

Core

870/C

Data Bus Width

8 bit

Data Ram Size

2 KB

Interface Type

SIO, UART

Maximum Clock Frequency

16 MHz

Number Of Programmable I/os

62

Number Of Timers

6

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Development Tools By Supplier

BM1040R0A, BMP86A100010A, BMP86A100010B, BMP86A200010B, BMP86A200020A, BMP86A300010A, BMP86A300020A, BMP86A300030A, SW89CN0-ZCC, SW00MN0-ZCC

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 8 Channel

For Use With

BM1401W0A-G - FLASH WRITER ON-BOARD PROGRAMTMP89C900XBG - EMULATION CHIP TMP89F LQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

TMP86FS28DFGJZ

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 92 of 272

- Download datasheet (3Mb)

7.1 Time Base Timer

Example :Set the time base timer frequency to fc/2

7.1.3 Function

Note 2: The interrupt frequency (TBTCK) must be selected with the time base timer disabled (TBTEN="0"). (The interrupt fre-

output of the timing generator which is selected by TBTCK. ) after time base timer has been enabled.

interrupt period ( Figure 7-2 ).

Table 7-1 Time Base Timer Interrupt Frequency ( Example : fc = 16.0 MHz, fs = 32.768 kHz )

An INTTBT ( Time Base Timer Interrupt ) is generated on the first falling edge of source clock ( The divider

The divider is not cleared by the program; therefore, only the first interrupt may be generated ahead of the set

quency must not be changed with the disable from the enable state.) Both frequency selection and enabling can be per-

formed simultaneously.

TBTCK

000

001

010

100

101

011

110

111

Source clock

TBTCR<TBTEN>

INTTBT

LD

LD

DI

SET

NORMAL1/2, IDLE1/2 Mode

Figure 7-2 Time Base Timer Interrupt

DV7CK = 0

(TBTCR) , 00000010B

(TBTCR) , 00001010B

(EIRL) . 6

1953.13

3906.25

244.14

976.56

7812.5

31250

1.91

7.63

Enable TBT

16

[Hz] and enable an INTTBT interrupt.

Time Base Timer Interrupt Frequency [Hz]

Page 80

NORMAL1/2, IDLE1/2 Mode

Interrupt period

DV7CK = 1

16384

1024

2048

4096

128

512

1

4

; TBTCK ← 010

; TBTEN ← 1

; IMF ← 0

SLOW1/2, SLEEP1/2 Mode

1

4

–

–

–

–

–

–

TMP86FS28DFG

Related parts for TMP86FS28DFG(JZ)

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Toshiba Semiconductor [TOSHIBA IGBT Module Silicon N Channel IGBT]

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR MODULE SILICON NPN TRIPLE DIFFUSED TYPE

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA INTELLIGENT POWER MODULE SILICON N CHANNEL LGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA IGBT Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR MODULE SILICON N−CHANNEL IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA INTELLIGENT POWER MODULE

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA IGBT Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

Toshiba Semiconductor [SILICON N CHANNEL 1GBT]

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet: