TMP86FS28DFG(JZ) Toshiba, TMP86FS28DFG(JZ) Datasheet - Page 54

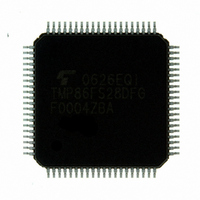

TMP86FS28DFG(JZ)

Manufacturer Part Number

TMP86FS28DFG(JZ)

Description

IC MCU 8BIT FLASH 60KB 80-LQFP

Manufacturer

Toshiba

Series

TLCS-870/Cr

Datasheet

1.TMP86FS28DFGJZ.pdf

(272 pages)

Specifications of TMP86FS28DFG(JZ)

Core Processor

870/C

Core Size

8-Bit

Speed

16MHz

Connectivity

SIO, UART/USART

Peripherals

LCD, PWM, WDT

Number Of I /o

62

Program Memory Size

60KB (60K x 8)

Program Memory Type

FLASH

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-LQFP

Processor Series

TLCS-870

Core

870/C

Data Bus Width

8 bit

Data Ram Size

2 KB

Interface Type

SIO, UART

Maximum Clock Frequency

16 MHz

Number Of Programmable I/os

62

Number Of Timers

6

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Development Tools By Supplier

BM1040R0A, BMP86A100010A, BMP86A100010B, BMP86A200010B, BMP86A200020A, BMP86A300010A, BMP86A300020A, BMP86A300030A, SW89CN0-ZCC, SW00MN0-ZCC

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 8 Channel

For Use With

BM1401W0A-G - FLASH WRITER ON-BOARD PROGRAMTMP89C900XBG - EMULATION CHIP TMP89F LQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

TMP86FS28DFGJZ

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 54 of 272

- Download datasheet (3Mb)

3.4 Software Interrupt (INTSW)

Example 2 :Restarting without returning interrupt

3.4 Software Interrupt (INTSW)

3.5 Undefined Instruction Interrupt (INTUNDEF)

3.6 Address Trap Interrupt (INTATRAP)

3.4.1 Address error detection

3.4.2 Debugging

is highest prioritized interrupt).

erated when the CPU fetches such a code and tries to execute it. INTUNDEF is accepted even if non-maskable inter-

rupt is in process. Contemporary process is broken and INTUNDEF interrupt process starts, soon after it is

requested.

trap interrupt (INTATRAP). INTATRAP is accepted even if non-maskable interrupt is in process. Contemporary pro-

cess is broken and INTATRAP interrupt process starts, soon after it is requested.

Executing the SWI instruction generates a software interrupt and immediately starts interrupt processing (INTSW

Use the SWI instruction only for detection of the address error or for debugging.

Taking code which is not defined as authorized instruction for instruction causes INTUNDEF. INTUNDEF is gen-

Note: The undefined instruction interrupt (INTUNDEF) forces CPU to jump into vector address, as software interrupt

Fetching instruction from unauthorized area for instructions (Address trapped area) causes reset output or address

Note: The operating mode under address trapped, whether to be reset output or interrupt processing, is selected on

(In this case, PSW (Includes IMF) before interrupt acceptance is discarded.)

rupt can be accepted immediately after the interrupt return instruction is executed.

memory address during single chip mode. Code FFH is the SWI instruction, so a software interrupt is gener-

ated and an address error is detected. The address error detection range can be further expanded by writing

FFH to unused areas of the program memory. Address trap reset is generated in case that an instruction is

fetched from RAM, DBR or SFR areas.

address.

Interrupt requests are sampled during the final cycle of the instruction being executed. Thus, the next inter-

Note 1: It is recommended that stack pointer be return to rate before INTATRAP (Increment 3 times), if return inter-

Note 2: When the interrupt processing time is longer than the interrupt request generation time, the interrupt service

FFH is read if for some cause such as noise the CPU attempts to fetch an instruction from a non-existent

Debugging efficiency can be increased by placing the SWI instruction at the software break point setting

(SWI) does.

watchdog timer control register (WDTCR).

PINTxx:

rupt instruction [RETN] is not utilized during interrupt service program under INTATRAP (such as Example

2).

task is performed but not the main task.

INC

INC

INC

(interrupt processing)

LD

JP

SP

SP

SP

EIRL, data

Restart Address

Page 42

;

;

; Set IMF to “1” or clear it to “0”

; Jump into restarting address

; Recover SP by 3

TMP86FS28DFG

Related parts for TMP86FS28DFG(JZ)

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Toshiba Semiconductor [TOSHIBA IGBT Module Silicon N Channel IGBT]

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR MODULE SILICON NPN TRIPLE DIFFUSED TYPE

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA INTELLIGENT POWER MODULE SILICON N CHANNEL LGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA IGBT Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR MODULE SILICON N−CHANNEL IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA INTELLIGENT POWER MODULE

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA IGBT Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

Toshiba Semiconductor [SILICON N CHANNEL 1GBT]

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet: