TMP86FS28DFG(JZ) Toshiba, TMP86FS28DFG(JZ) Datasheet - Page 24

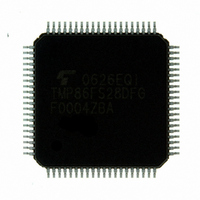

TMP86FS28DFG(JZ)

Manufacturer Part Number

TMP86FS28DFG(JZ)

Description

IC MCU 8BIT FLASH 60KB 80-LQFP

Manufacturer

Toshiba

Series

TLCS-870/Cr

Datasheet

1.TMP86FS28DFGJZ.pdf

(272 pages)

Specifications of TMP86FS28DFG(JZ)

Core Processor

870/C

Core Size

8-Bit

Speed

16MHz

Connectivity

SIO, UART/USART

Peripherals

LCD, PWM, WDT

Number Of I /o

62

Program Memory Size

60KB (60K x 8)

Program Memory Type

FLASH

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-LQFP

Processor Series

TLCS-870

Core

870/C

Data Bus Width

8 bit

Data Ram Size

2 KB

Interface Type

SIO, UART

Maximum Clock Frequency

16 MHz

Number Of Programmable I/os

62

Number Of Timers

6

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Development Tools By Supplier

BM1040R0A, BMP86A100010A, BMP86A100010B, BMP86A200010B, BMP86A200020A, BMP86A300010A, BMP86A300020A, BMP86A300030A, SW89CN0-ZCC, SW00MN0-ZCC

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 8 Channel

For Use With

BM1401W0A-G - FLASH WRITER ON-BOARD PROGRAMTMP89C900XBG - EMULATION CHIP TMP89F LQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

TMP86FS28DFGJZ

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 24 of 272

- Download datasheet (3Mb)

2.2 System Clock Controller

High-frequency

Low-frequency

2.2.2 Timing Generator

2.2.2.1

clock fc

clock fs

SYSCK

DV7CK

from the basic clock (fc or fs). The timing generator provides the following functions.

The timing generator generates the various system clocks supplied to the CPU core and peripheral hardware

and machine cycle counters.

TBTCR<DV7CK>, that is shown in Figure 2-4. As reset and STOP mode started/canceled, the prescaler

and the divider are cleared to “0”.

1. Generation of main system clock

2. Generation of divider output (

3. Generation of source clocks for time base timer

4. Generation of source clocks for watchdog timer

5. Generation of internal source clocks for timer/counters

6. Generation of warm-up clocks for releasing STOP mode

7. LCD

Configuration of timing generator

The timing generator consists of a 2-stage prescaler, a 21-stage divider, a main system clock generator,

An input clock to the 7th stage of the divider depends on the operating mode, SYSCR2<SYSCK> and

Timer counter, Serial interface, Time-base-timer, divider output, etc. (Peripheral functions)

1

2

fc/4

Main system clock generator

Figure 2-4 Configuration of Timing Generator

1

2

3

4

5 6

DVO

plexer

Multi-

A

B

) pulses

S

Page 12

Y

7

fc or fs

8

9

10

11

12

13

Divider

14

Machine cycle counters

15

16

17 18 19 20 21

B0

B1

A0 Y0

A1 Y1

TMP86FS28DFG

S

Multiplexer

Warm-up

controller

Watchdog

timer

Related parts for TMP86FS28DFG(JZ)

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Toshiba Semiconductor [TOSHIBA IGBT Module Silicon N Channel IGBT]

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR MODULE SILICON NPN TRIPLE DIFFUSED TYPE

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA INTELLIGENT POWER MODULE SILICON N CHANNEL LGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA IGBT Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR MODULE SILICON N−CHANNEL IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA GTR Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA INTELLIGENT POWER MODULE

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA IGBT Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

TOSHIBA Intelligent Power Module Silicon N Channel IGBT

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet:

Part Number:

Description:

Toshiba Semiconductor [SILICON N CHANNEL 1GBT]

Manufacturer:

TOSHIBA Semiconductor CORPORATION

Datasheet: